CD74HC138

CD74HC138 is High-Speed CMOS Logic 3 to 8-Line Decoder/Demultiplexer Inverting/Noninverting manufactured by Texas Instruments.

CD54HC138, CD74HC138, CD54HCT138, CD74HCT138, CD54HC238, CD74HC238, CD54HCT238, CD74HCT238

SCHS147J

- NOVEMBER 1998

- REVISED NOVEMBER 2021

CDx4HC138, CDx4HCT138, CDx4HC238, CDx4HCT238 High-Speed CMOS Logic 3- to 8-Line Decoder/Demultiplexer Inverting and Noninverting

1 Features

- Select one of eight data outputs:

- Active low for '138

- Active high for '238

- l/O port or memory selector

- Three enable inputs to simplify cascading

- Typical propagation delay of 13 ns at VCC = 5 V, CL = 15 p F, TA = 25°C

- Fanout (over temperature range)

- Bus driver outputs: 15 LSTTL loads

- Standard outputs: 10 LSTTL loads

- Wide operating temp range: -55°C to 125°C

- Balanced propagation delay and transition times

- Significant power reduction pared to LSTTL logic ICs

- HC types

- 2 V to 6 V operation

- High noise immunity: NIL = 30%, NIH = 30% of

VCC at VCC = 5 V

- HCT types

- 4.5-V to 5.5-V operation

- Direct LSTTL input logic patibility, VIL= 0.8

V (Max), VIH = 2 V (Min)

- CMOS input patibility, Il ≤ 1µA at VOL, VOH

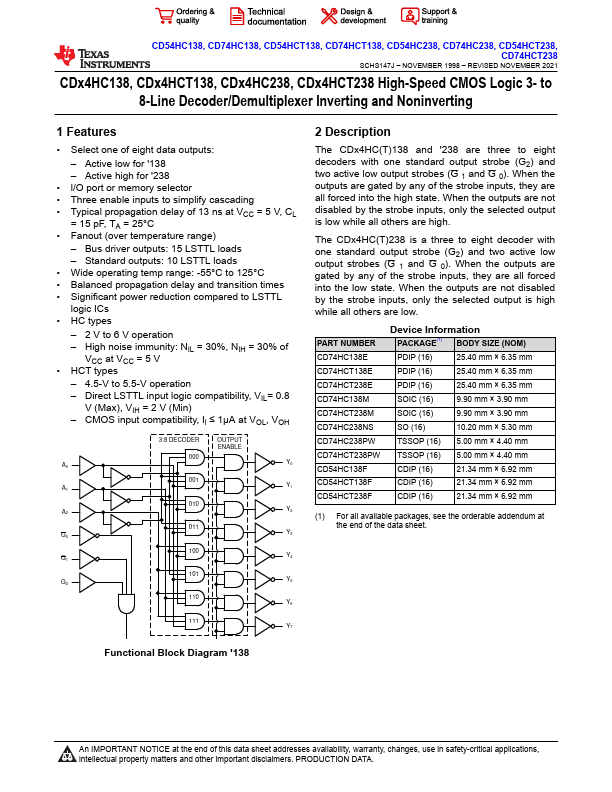

3:8 DECODER

OUTPUT...