CD74HC4017-Q1

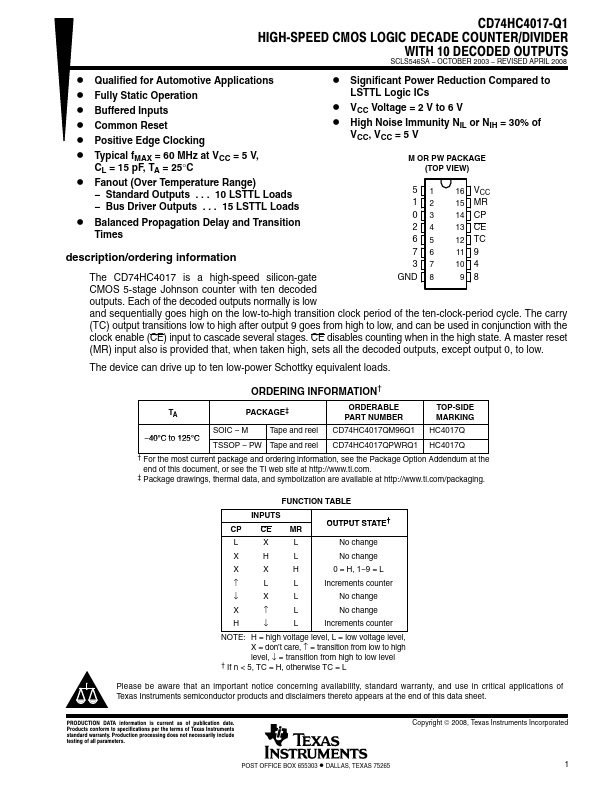

CD74HC4017-Q1 is HIGH-SPEED CMOS LOGIC DECADE COUNTER/DIVIDER manufactured by Texas Instruments.

description

/ordering information

76 37

11 9 10 4

The CD74HC4017 is a high-speed silicon-gate

GND 8

CMOS 5-stage Johnson counter with ten decoded outputs. Each of the decoded outputs normally is low and sequentially goes high on the low-to-high transition clock period of the ten-clock-period cycle. The carry

(TC) output transitions low to high after output 9 goes from high to low, and can be used in conjunction with the clock enable (CE) input to cascade several stages. CE disables counting when in the high state. A master reset

(MR) input also is provided that, when taken high, sets all the decoded outputs, except output 0, to low.

The device can drive up to ten low-power Schottky equivalent loads.

ORDERING INFORMATION{

PACKAGE‡

ORDERABLE PART NUMBER

TOP-SIDE MARKING

- 40°C to 125°C

SOIC

- M

Tape and reel

TSSOP

- PW Tape and reel

CD74HC4017QM96Q1 HC4017Q CD74HC4017QPWRQ1 HC4017Q

† For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at http://.ti.. ‡ Package drawings, thermal data, and symbolization are available at http://.ti./packaging.

FUNCTION TABLE

INPUTS CP CE MR

OUTPUT STATE†

No change

No change

0 = H, 1- 9 = L

↑ L L Increments counter

↓XL

No change

X↑ L

No change

H ↓ L Increments counter

NOTE: H = high voltage level, L = low voltage...