CDCLVP1204

Description

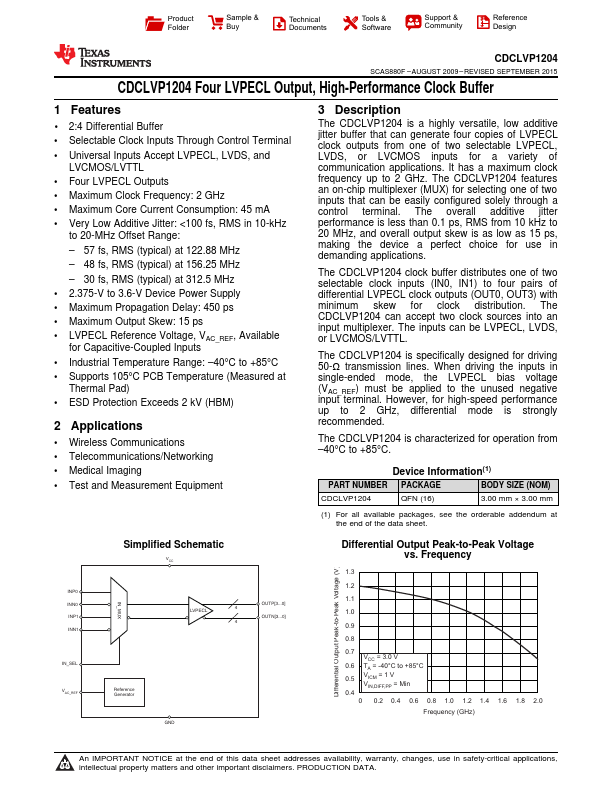

The CDCLVP1204 is a highly versatile, low additive jitter buffer that can generate four copies of LVPECL clock outputs from one of two selectable LVPECL, LVDS, or LVCMOS inputs for a variety of munication applications.

Key Features

- 1 2:4 Differential Buffer

- Selectable Clock Inputs Through Control Terminal

- Universal Inputs Accept LVPECL, LVDS, and

- Four LVPECL Outputs

- Maximum Clock Frequency: 2 GHz

Applications

- Wireless munications