DS90C241

Description

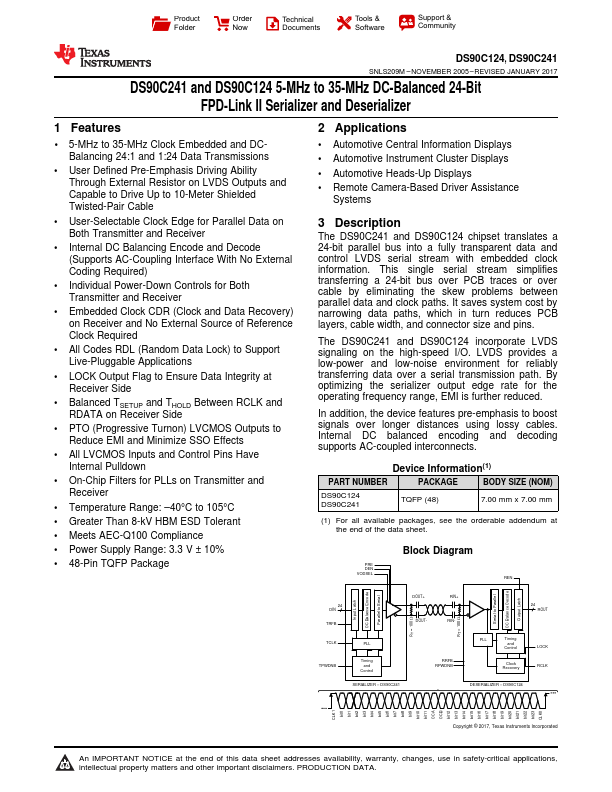

The DS90C241 and DS90C124 chipset translates a 24-bit parallel bus into a fully transparent data and control LVDS serial stream with embedded clock information.

Key Features

- User-Selectable Clock Edge for Parallel Data on Both Transmitter and Receiver

- Internal DC Balancing Encode and Decode (Supports AC-Coupling Interface With No External Coding Required)

- Individual Power-Down Controls for Both Transmitter and Receiver

- Embedded Clock CDR (Clock and Data Recovery) on Receiver and No External Source of Reference Clock Required

- All Codes RDL (Random Data Lock) to Support Live-Pluggable Applications

- LOCK Output Flag to Ensure Data Integrity at Receiver Side

- Balanced TSETUP and THOLD Between RCLK and RDATA on Receiver Side

- PTO (Progressive Turnon) LVCMOS Outputs to Reduce EMI and Minimize SSO Effects

- All LVCMOS Inputs and Control Pins Have Internal Pulldown

- On-Chip Filters for PLLs on Transmitter and Receiver