DS90CF364A

Description

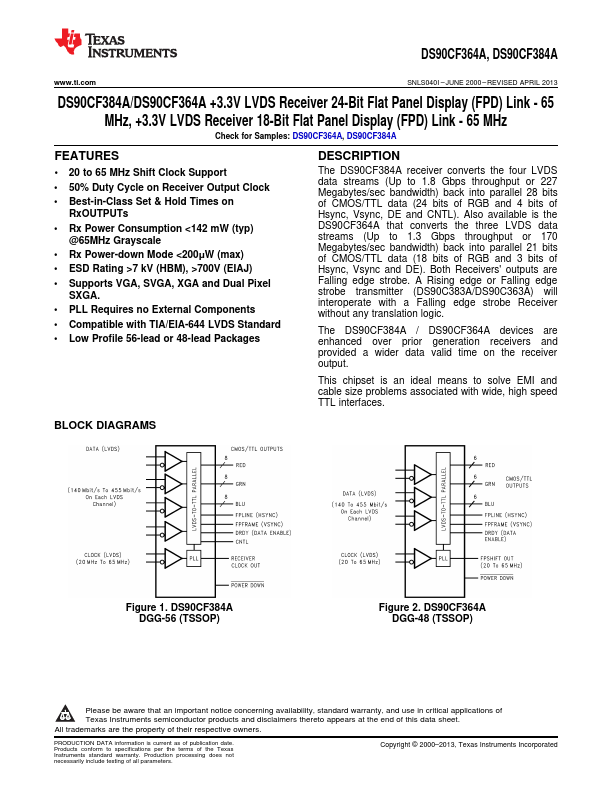

The DS90CF384A receiver converts the four LVDS data streams (Up to 1.8 Gbps throughput or 227 Megabytes/sec bandwidth) back into parallel 28 bits of CMOS/TTL data (24 bits of RGB and 4 bits of Hsync, Vsync, DE and CNTL).

Key Features

- 2 20 to 65 MHz Shift Clock Support

- 50% Duty Cycle on Receiver Output Clock

- Best-in-Class Set & Hold Times on RxOUTPUTs

- Rx Power Consumption <142 mW (typ) @65MHz Grayscale

- Rx Power-down Mode <200μW (max)

- ESD Rating >7 kV (HBM), >700V (EIAJ)

- Supports VGA, SVGA, XGA and Dual Pixel SXGA

- Low Profile 56-lead or 48-lead Packages