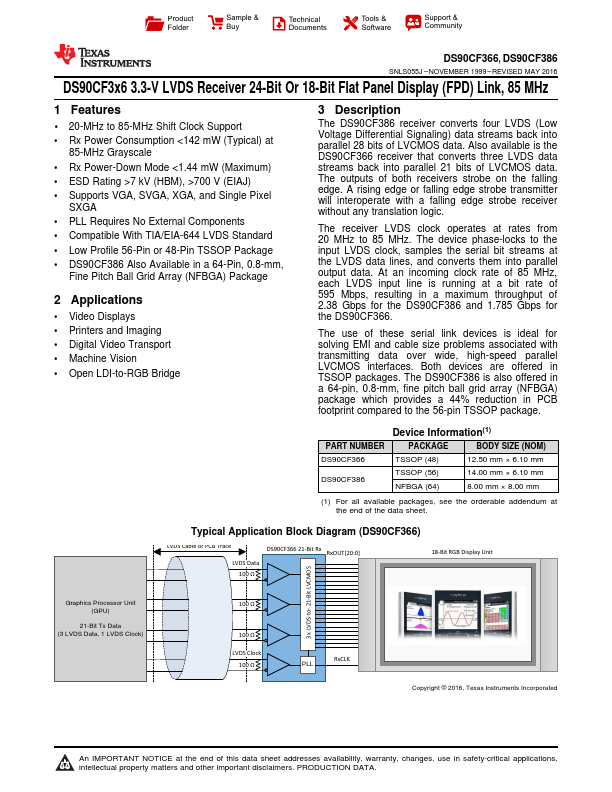

DS90CF366

Description

The DS90CF386 receiver converts four LVDS (Low Voltage Differential Signaling) data streams back into parallel 28 bits of LVCMOS data.

Key Features

- 1 20-MHz to 85-MHz Shift Clock Support

- Rx Power Consumption <142 mW (Typical) at 85-MHz Grayscale

- Rx Power-Down Mode <1.44 mW (Maximum)

- ESD Rating >7 kV (HBM), >700 V (EIAJ)

- Supports VGA, SVGA, XGA, and Single Pixel SXGA

- Low Profile 56-Pin or 48-Pin TSSOP Package

- DS90CF386 Also Available in a 64-Pin, 0.8-mm, Fine Pitch Ball Grid Array (NFBGA) Package