DS90CF563

Description

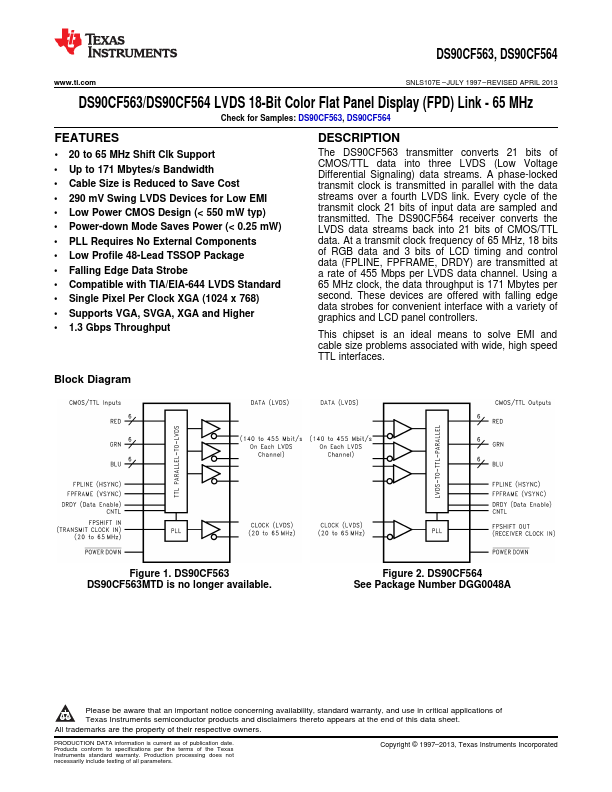

The DS90CF563 transmitter converts 21 bits of CMOS/TTL data into three LVDS (Low Voltage Differential Signaling) data streams.

Key Features

- 2 20 to 65 MHz Shift Clk Support

- Up to 171 Mbytes/s Bandwidth

- Cable Size is Reduced to Save Cost

- 290 mV Swing LVDS Devices for Low EMI

- Low Power CMOS Design (< 550 mW typ)

- Power-down Mode Saves Power (< 0.25 mW)

- Low Profile 48-Lead TSSOP Package

- Falling Edge Data Strobe

- Single Pixel Per Clock XGA (1024 x

- Supports VGA, SVGA, XGA and Higher