DS90UR241-Q1

Description

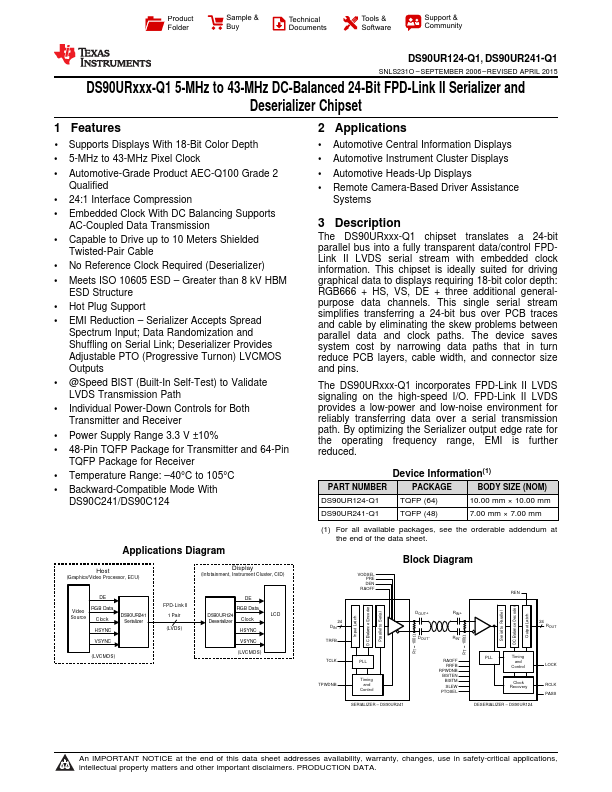

The DS90URxxx-Q1 chipset translates a 24-bit parallel bus into a fully transparent data/control FPDLink II LVDS serial stream with embedded clock information.

Key Features

- 1 Supports Displays With 18-Bit Color Depth

- 5-MHz to 43-MHz Pixel Clock

- Automotive-Grade Product AEC-Q100 Grade 2 Qualified

- 24:1 Interface pression

- Embedded Clock With DC Balancing Supports AC-Coupled Data Transmission

- Capable to Drive up to 10 Meters Shielded Twisted-Pair Cable

- No Reference Clock Required (Deserializer)

- Meets ISO 10605 ESD - Greater than 8 kV HBM ESD Structure

- Hot Plug Support

- @Speed BIST (Built-In Self-Test) to Validate LVDS Transmission Path