DS92LV040A

Description

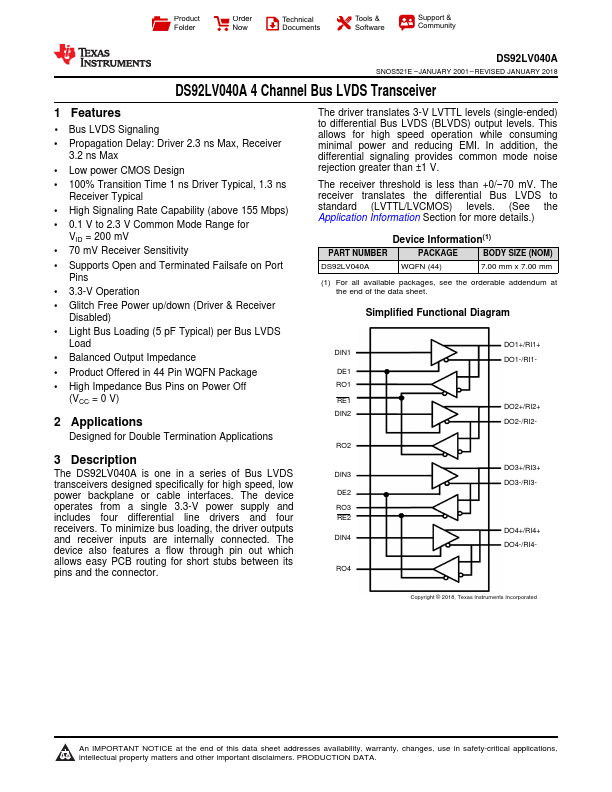

The DS92LV040A is one in a series of Bus LVDS transceivers designed specifically for high speed, low power backplane or cable interfaces.

Key Features

- 1 Bus LVDS Signaling

- Propagation Delay: Driver 2.3 ns Max, Receiver

- Low power CMOS Design

- 100% Transition Time 1 ns Driver Typical, 1.3 ns

- High Signaling Rate Capability (above 155 Mbps)

- 70 mV Receiver Sensitivity

- Supports Open and Terminated Failsafe on Port

- 3.3-V Operation

- Glitch Free Power up/down (Driver & Receiver

- Light Bus Loading (5 pF Typical) per Bus LVDS