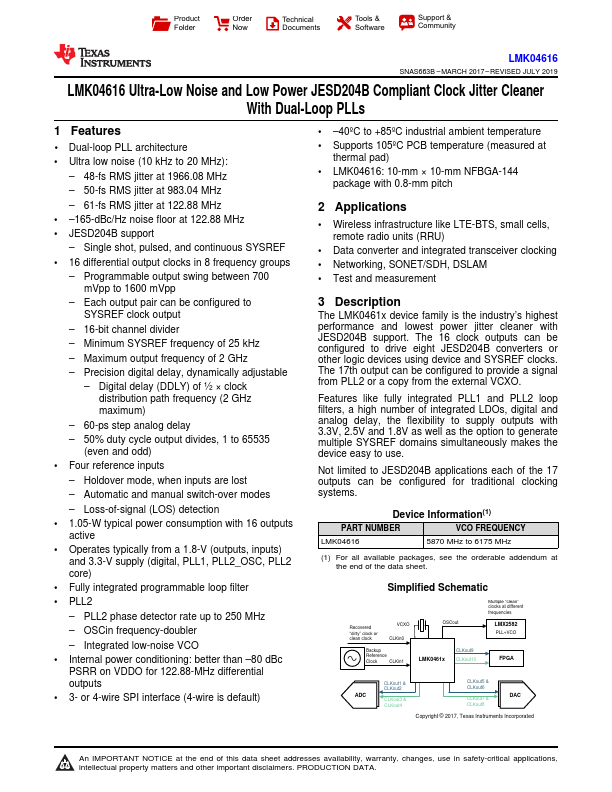

LMK04616

Overview

- 1 Dual-loop PLL architecture

- Ultra low noise (10 kHz to 20 MHz): - 48-fs RMS jitter at 1966.08 MHz - 50-fs RMS jitter at 983.04 MHz - 61-fs RMS jitter at 122.88 MHz

- -165-dBc/Hz noise floor at 122.88 MHz

- JESD204B support - Single shot, pulsed, and continuous SYSREF

- 16 differential output clocks in 8 frequency groups - Programmable output swing between 700 mVpp to 1600 mVpp - Each output pair can be configured to SYSREF clock output - 16-bit channel divider - Minimum SYSREF frequency of 25 kHz - Maximum output frequency of 2 GHz - Precision digital delay, dynamically adjustable - Digital delay (DDLY) of ½ × clock distribution path frequency (2 GHz maximum) - 60-ps step analog delay - 50% duty cycle output divides, 1 to 65535 (even and odd)

- Four reference inputs - Holdover mode, when inputs are lost - Automatic and manual switch-over modes - Loss-of-signal (LOS) detection

- 1.05-W typical power consumption with 16 outputs active

- Operates typically from a 1.8-V (outputs, inputs) and 3.3-V supply (digital, PLL1, PLL2_OSC, PLL2 core)

- Fully integrated programmable loop filter

- PLL2 - PLL2 phase detector rate up to 250 MHz - OSCin frequency-doubler - Integrated low-noise VCO