LMK05028

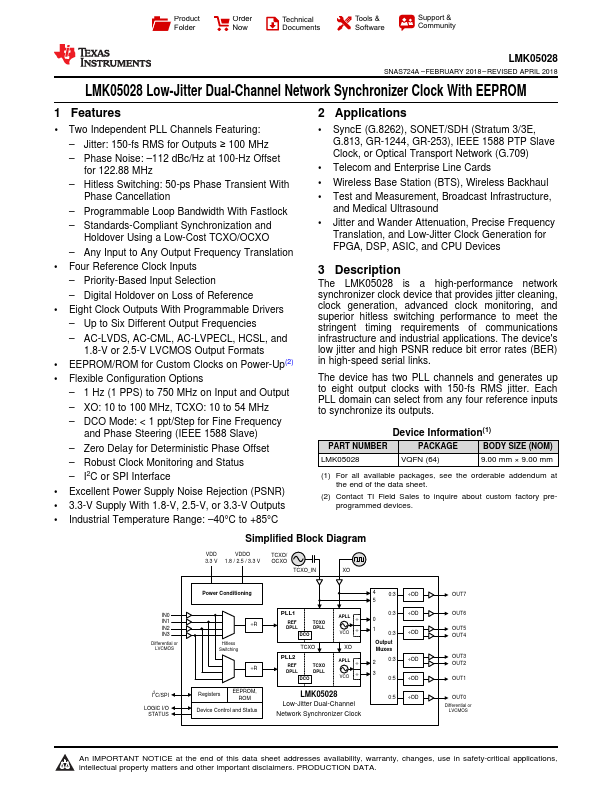

LMK05028 is Low-Jitter Dual-Channel Network Synchronizer Clock manufactured by Texas Instruments.

Product Folder

Order Now

Technical Documents

Tools & Software

Support & munity

SNAS724A

- FEBRUARY 2018

- REVISED APRIL 2018

LMK05028 Low-Jitter Dual-Channel Network Synchronizer Clock With EEPROM

1 Features

- 1 Two Independent PLL Channels Featuring:

- Jitter: 150-fs RMS for Outputs ≥ 100 MHz

- Phase Noise:

- 112 dBc/Hz at 100-Hz Offset for 122.88 MHz

- Hitless Switching: 50-ps Phase Transient With Phase Cancellation

- Programmable Loop Bandwidth With Fastlock

- Standards-pliant Synchronization and Holdover Using a Low-Cost TCXO/OCXO

- Any Input to Any Output Frequency Translation

- Four Reference Clock Inputs

- Priority-Based Input Selection

- Digital Holdover on Loss...