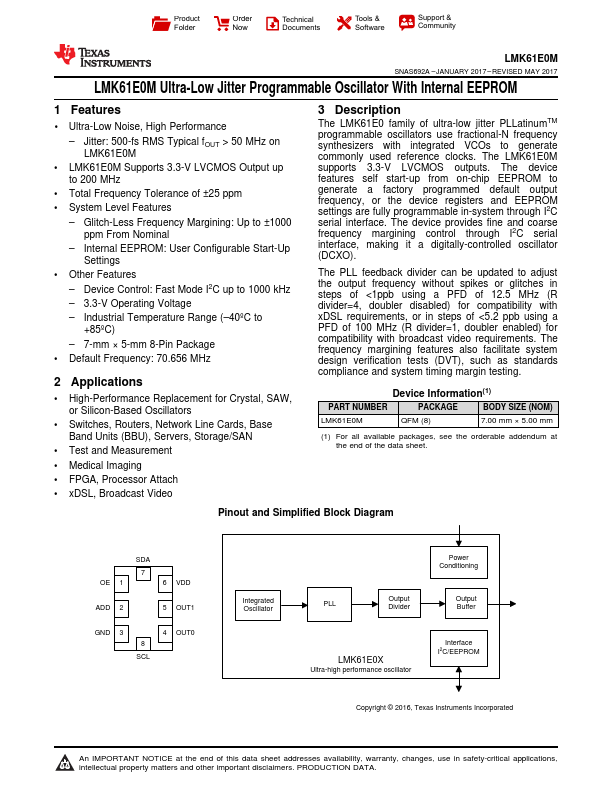

LMK61E0M Description

The LMK61E0 family of ultra-low jitter PLLatinumTM programmable oscillators use fractional-N frequency synthesizers with integrated VCOs to generate monly used reference clocks. The LMK61E0M supports 3.3-V LVCMOS outputs.

LMK61E0M Key Features

- 1 Ultra-Low Noise, High Performance

- Jitter: 500-fs RMS Typical fOUT > 50 MHz on LMK61E0M

- LMK61E0M Supports 3.3-V LVCMOS Output up to 200 MHz

- Total Frequency Tolerance of ±25 ppm

- System Level Features

- Glitch-Less Frequency Margining: Up to ±1000 ppm From Nominal

- Internal EEPROM: User Configurable Start-Up Settings

- Other Features

- Device Control: Fast Mode I2C up to 1000 kHz

- 3.3-V Operating Voltage

LMK61E0M Applications

- High-Performance Replacement for Crystal, SAW, or Silicon-Based Oscillators