OMAPL138B-EP

Overview

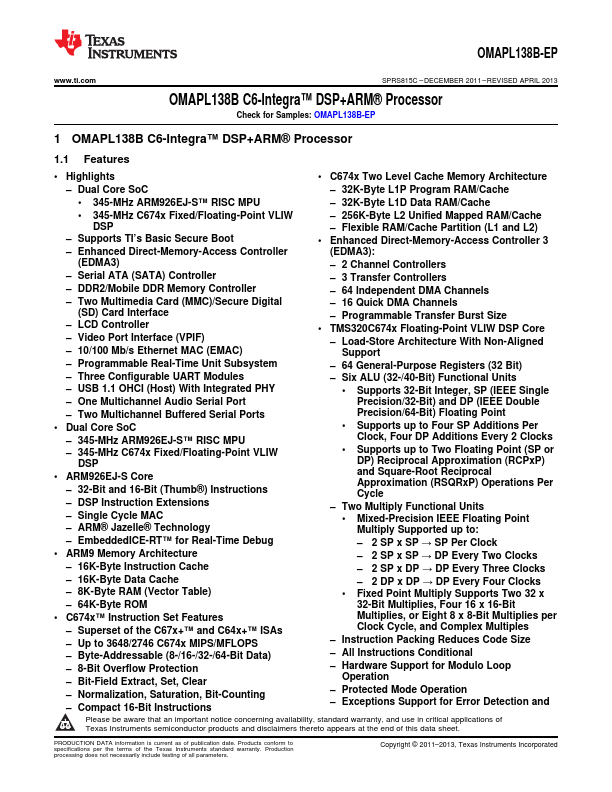

- Highlights

- C674x Two Level Cache Memory Architecture - Dual Core SoC - 32K-Byte L1P Program RAM/Cache

- 345-MHz ARM926EJ-S™ RISC MPU - 32K-Byte L1D Data RAM/Cache

- 345-MHz C674x Fixed/Floating-Point VLIW - 256K-Byte L2 Unified Mapped RAM/Cache DSP - Flexible RAM/Cache Partition (L1 and L2) - Supports TI’s Basic Secure Boot

- Enhanced Direct-Memory-Access Controller 3 - Enhanced Direct-Memory-Access Controller (EDMA3): (EDMA3) - 2 Channel Controllers - Serial ATA (SATA) Controller - 3 Transfer Controllers - DDR2/Mobile DDR Memory Controller - 64 Independent DMA Channels - Two Multimedia Card (MMC)/Secure Digital (SD) Card Interface - LCD Controller - Video Port Interface (VPIF) - 10/100 Mb/s Ethernet MAC (EMAC) - 16 Quick DMA Channels - Programmable Transfer Burst Size

- TMS320C674x Floating-Point VLIW DSP Core - Load-Store Architecture With Non-Aligned Support - Programmable Real-Time Unit Subsystem - 64 General-Purpose Registers (32 Bit) - Three Configurable UART Modules - Six ALU (32-/40-Bit) Functional Units - USB 1.1 OHCI (Host) With Integrated PHY

- Supports 32-Bit Integer, SP (IEEE Single - One Multichannel Audio Serial Port Precision/32-Bit) and DP (IEEE Double - Two Multichannel Buffered Serial Ports Precision/64-Bit) Floating Point

- Dual Core SoC - 345-MHz ARM926EJ-S™ RISC MPU - 345-MHz C674x Fixed/Floating-Point VLIW DSP

- ARM926EJ-S Core - 32-Bit and 16-Bit (Thumb®) Instructions - DSP Instruction Extensions - Single Cycle MAC - ARM® Jazelle® Technology - EmbeddedICE-RT™ for Real-Time Debug

- ARM9 Memory Architecture - 16K-Byte Instruction Cache - 16K-Byte Data Cache - 8K-Byte RAM (Vector Table) - 64K-By