PLL1707-Q1 Overview

Description

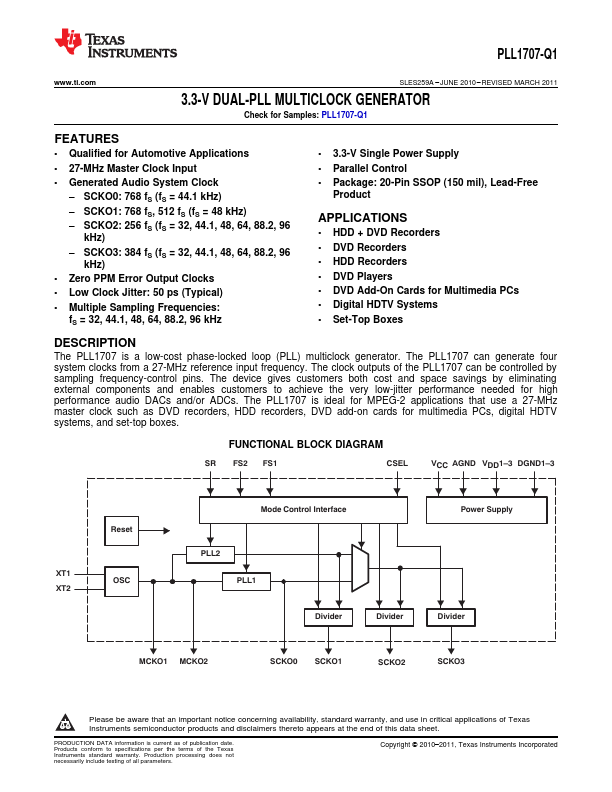

The PLL1707 is a low-cost phase-locked loop (PLL) multiclock generator. The PLL1707 can generate four system clocks from a 27-MHz reference input frequency.

Key Features

- Qualified for Automotive Applications

- 27-MHz Master Clock Input

- Zero PPM Error Output Clocks

- Low Clock Jitter: 50 ps (Typical)

- Multiple Sampling Frequencies: fS = 32, 44.1, 48, 64, 88.2, 96 kHz