SN10KHT5574

Overview

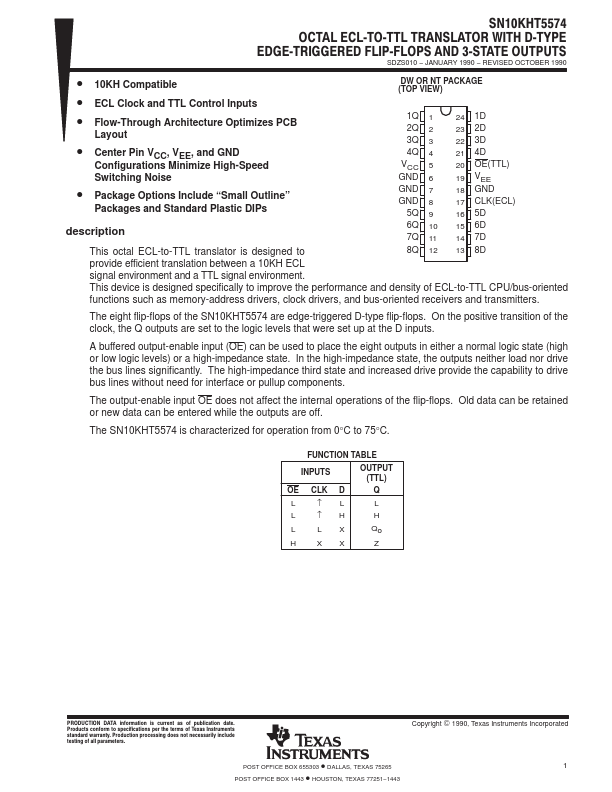

6Q 10 7Q 11 15 6D 14 7D This octal ECL-to-TTL translator is designed to 8Q 12 13 8D provide efficient translation between a 10KH ECL signal environment and a TTL signal environment. This device is designed specifically to improve the performance and density of ECL-to-TTL CPU/bus-oriented functions such as memory-address drivers, clock drivers, and bus-oriented receivers and transmitters.