SN54ABT162841 Overview

Key Features

- noninverting 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads

- They are particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers

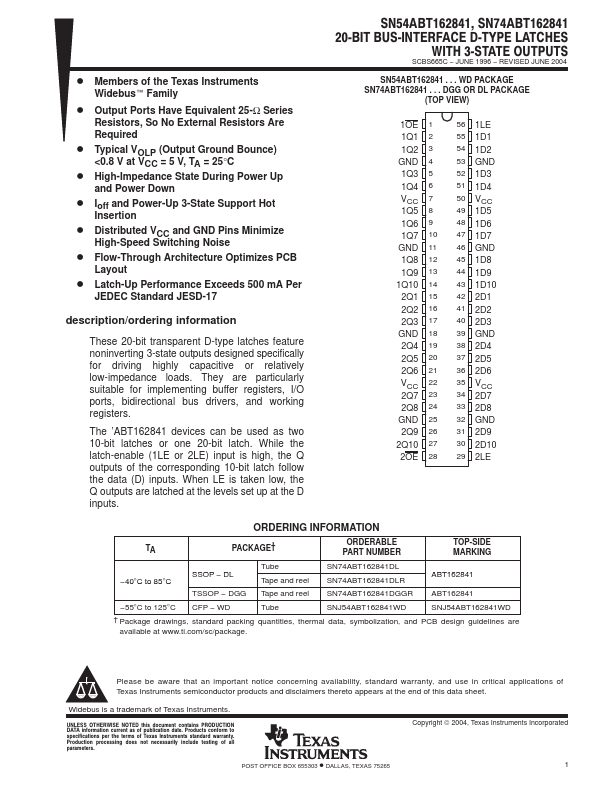

- The ’ABT162841 devices can be used as two 10-bit latches or one 20-bit latch

- While the latch-enable (1LE or 2LE) input is high, the Q outputs of the corresponding 10-bit latch follow the data (D) inputs

- When LE is taken low, the Q outputs are latched at the levels set up at the D inputs