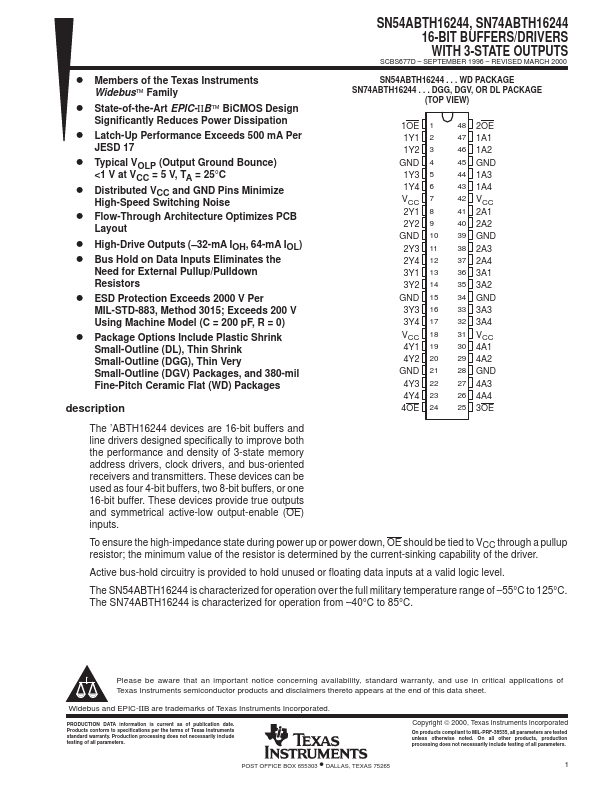

| Part | SN54ABTH16244 |

|---|---|

| Description | 16-BIT BUFFERS/DRIVERS |

| Manufacturer | Texas Instruments |

| Size | 504.93 KB |

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| No distributor offers were returned for this part. | |||

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| MAX232 | Maxim Integrated | Multichannel RS-232 Drivers/Receivers |

| SIM6892M | Sanken | 600V High Voltage 3-phase Motor Drivers |

| TMC2209 | TRINAMIC | Step/Dir Drivers |