SN54BCT25244 Overview

Description

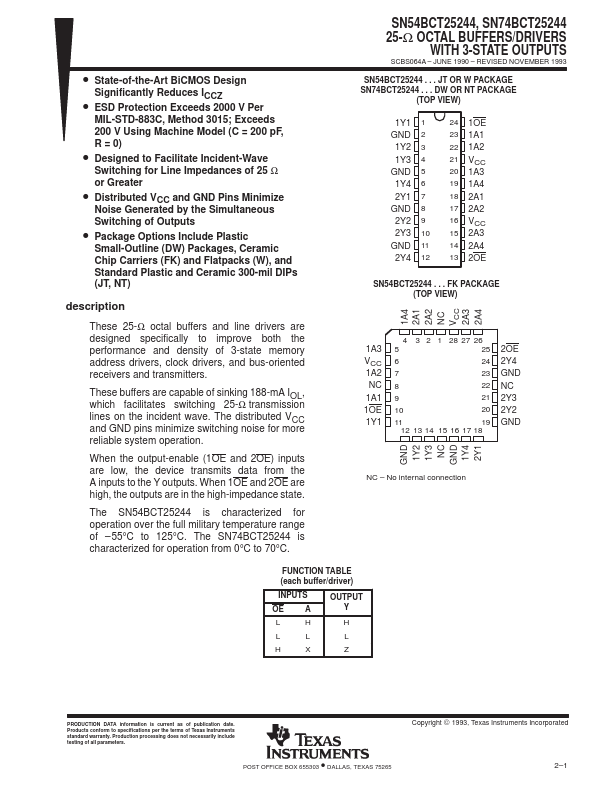

These 25-Ω octal buffers and line drivers are designed specifically to improve both the performance and density of 3-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters. These buffers are capable of sinking 188-mA IOL, which facilitates switching 25-Ω transmission lines on the incident wave.