SN65EPT22 Overview

Key Specifications

Package: SOIC

Pins: 8

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

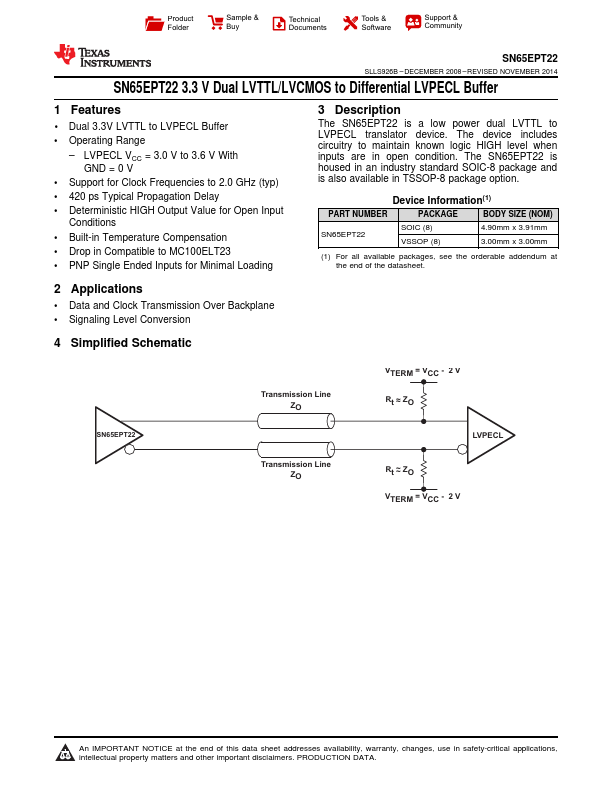

The SN65EPT22 is a low power dual LVTTL to LVPECL translator device. The device includes circuitry to maintain known logic HIGH level when inputs are in open condition.

Key Features

- 1 Dual 3.3V LVTTL to LVPECL Buffer

- Operating Range – LVPECL VCC = 3.0 V to 3.6 V With GND = 0 V

- Support for Clock Frequencies to 2.0 GHz (typ)

- 420 ps Typical Propagation Delay

- Deterministic HIGH Output Value for Open Input Conditions