SN65LV1023A-EP Overview

Description

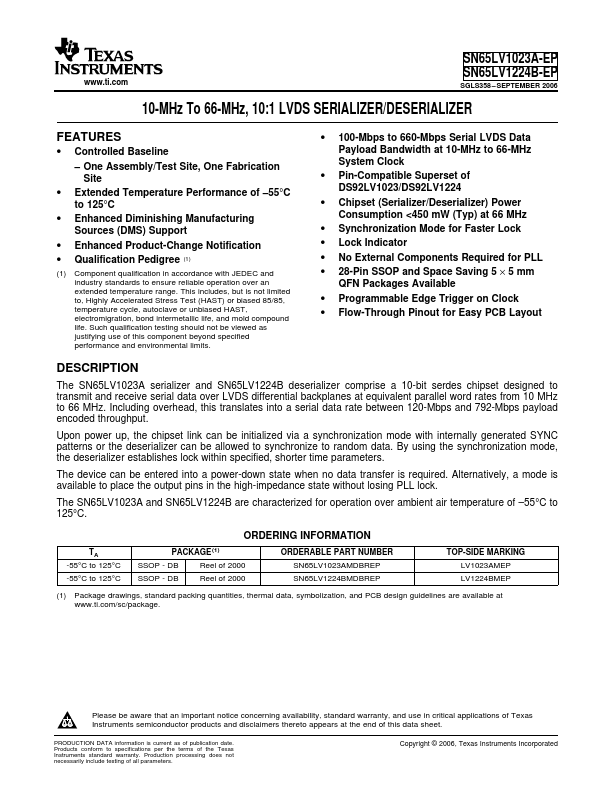

The SN65LV1023A serializer and SN65LV1224B deserializer comprise a 10-bit serdes chipset designed to transmit and receive serial data over LVDS differential backplanes at equivalent parallel word rates from 10 MHz to 66 MHz. Including overhead, this translates into a serial data rate between 120-Mbps and 792-Mbps payload encoded throughput.

Key Features

- Controlled Baseline – One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of –55°C to 125°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- 100-Mbps to 660-Mbps Serial LVDS Data Payload Bandwidth at 10-MHz to 66-MHz System Clock