SN65LVDS116 Overview

Key Specifications

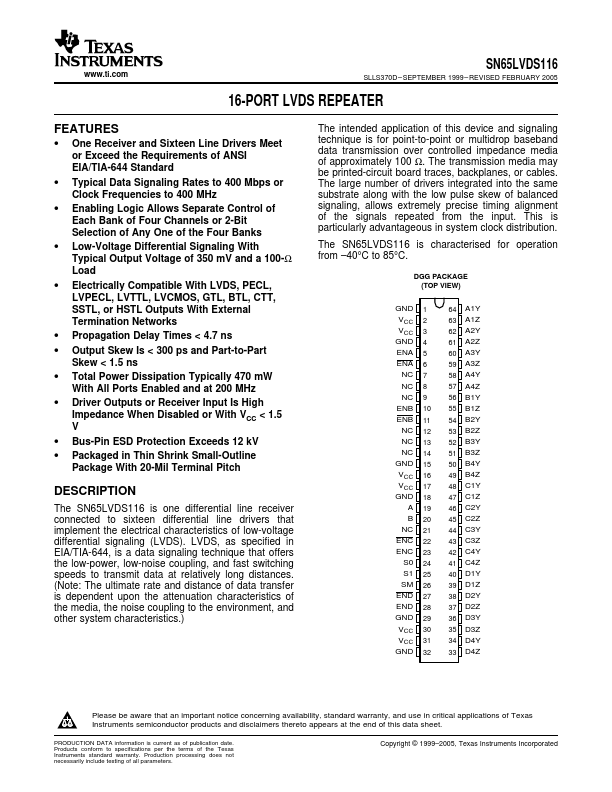

Package: TSSOP

Mount Type: Surface Mount

Pins: 64

Operating Voltage: 3.3 V

Description

The SN65LVDS116 is one differential line receiver connected to sixteen differential line drivers that implement the The intended application of this device and signaling technique is for point-to-point or multidrop baseband data transmission over controlled impedance media of approximately 100 Ω. The transmission media may be printed-circuit board traces, backplanes, or cables.

Key Features

- One Receiver and Sixteen Line Drivers Meet or Exceed the Requirements of ANSI EIA/TIA-644 Standard

- Typical Data Signaling Rates to 400 Mbps or Clock Frequencies to 400 MHz

- Enabling Logic Allows Separate Control of Each Bank of Four Channels or 2-Bit Selection of Any One of the Four Banks

- Low-Voltage Differential Signaling With Typical Output Voltage of 350 mV and a 100-Ω Load

- Electrically Compatible With LVDS, PECL, LVPECL, LVTTL, LVCMOS, GTL, BTL, CTT, SSTL, or HSTL Outputs With External Termination Networks