SN65LVDS18

Description

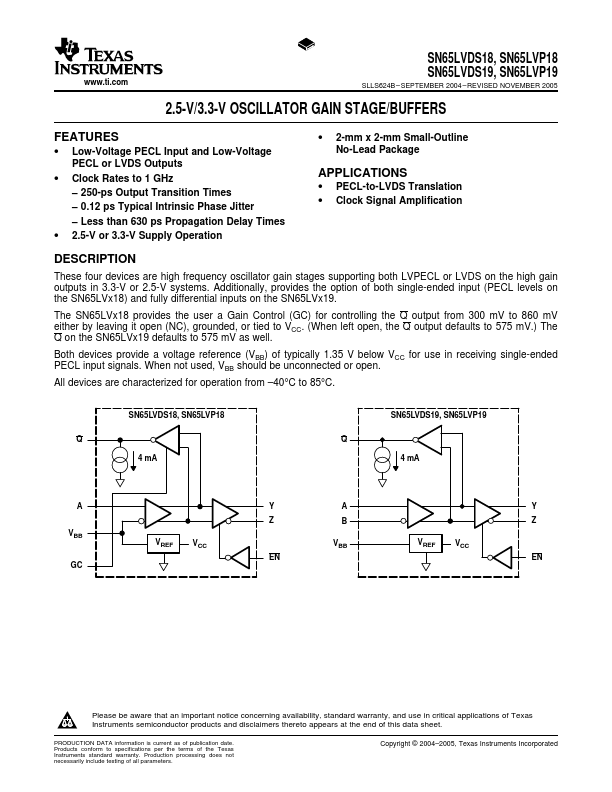

These four devices are high frequency oscillator gain stages supporting both LVPECL or LVDS on the high gain outputs in 3.3-V or 2.5-V systems. Additionally, provides the option of both single-ended input (PECL levels on the SN65LVx18) and fully differential inputs on the SN65LVx19.

Key Features

- Low-Voltage PECL Input and Low-Voltage PECL or LVDS Outputs

- Clock Rates to 1 GHz – 250-ps Output Transition Times – 0.12 ps Typical Intrinsic Phase Jitter – Less than 630 ps Propagation Delay Times

- 2.5-V or 3.3-V Supply Operation

- 2-mm x 2-mm Small-Outline No-Lead Package