SN65LVDS94 Overview

Key Specifications

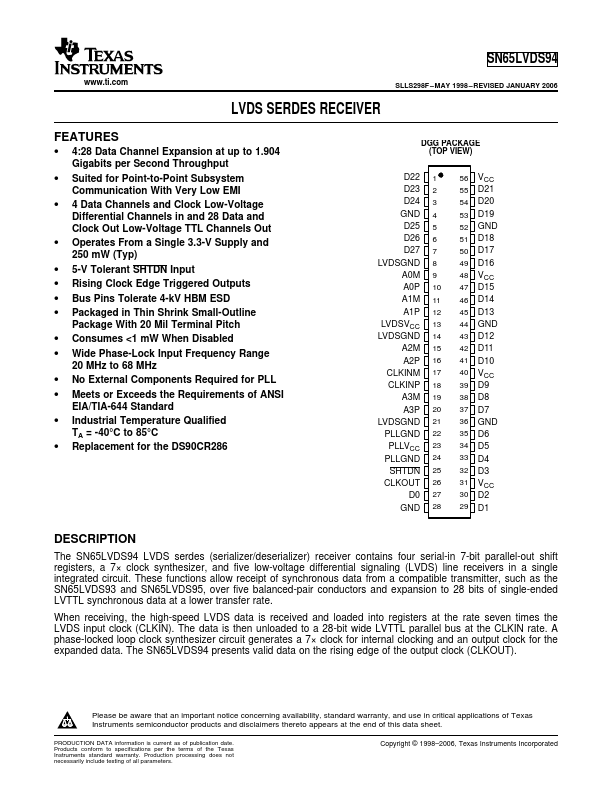

Package: TSSOP

Pins: 56

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.6 V

Description

The SN65LVDS94 LVDS serdes (serializer/deserializer) receiver contains four serial-in 7-bit parallel-out shift registers, a 7× clock synthesizer, and five low-voltage differential signaling (LVDS) line receivers in a single integrated circuit. These functions allow receipt of synchronous data from a compatible transmitter, such as the SN65LVDS93 and SN65LVDS95, over five balanced-pair conductors and expansion to 28 bits of single-ended LVTTL synchronous data at a lower transfer rate.

Key Features

- 4:28 Data Channel Expansion at up to 1.904 Gigabits per Second Throughput

- Suited for Point-to-Point Subsystem Communication With Very Low EMI

- 4 Data Channels and Clock Low-Voltage Differential Channels in and 28 Data and Clock Out Low-Voltage TTL Channels Out

- Operates From a Single 3.3-V Supply and 250 mW (Typ)

- 5-V Tolerant SHTDN Input