SN74AHC74Q-Q1

SN74AHC74Q-Q1 is Dual Positive-Edge-Triggered D-Type Flip-Flop manufactured by Texas Instruments.

SN74AHC74QĆQ1 DUAL POSITIVEĆEDGEĆTRIGGERED DĆTYPE FLIPĆFLOP

WITH CLEAR AND PRESET

SGDS020A

- FEBRUARY 2002

- REVISED APRIL 2008

D Qualified for Automotive Applications D EPIC (Enhanced-Performance Implanted

CMOS) Process

D Operating Range 2-V to 5.5-V VCC D Latch-Up Performance Exceeds 250 m A Per

JESD 17

D ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 p F, R = 0)

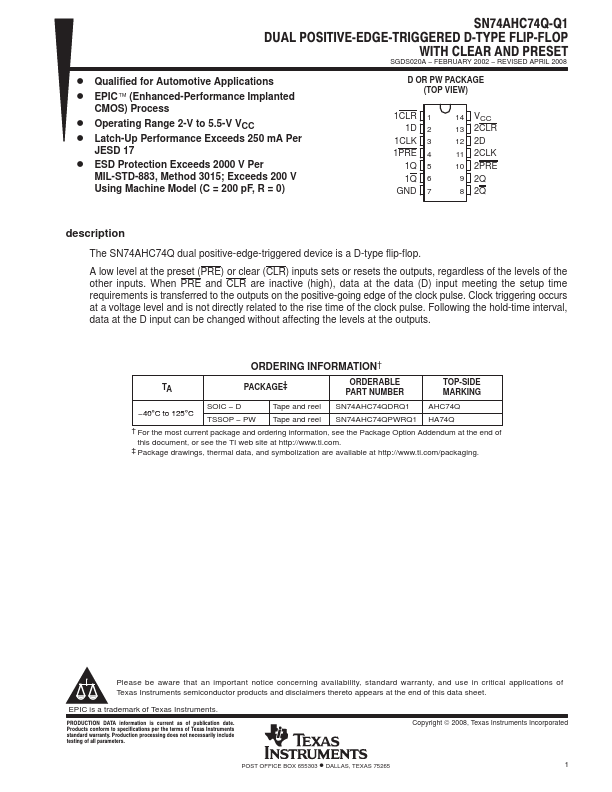

D OR PW PACKAGE (TOP VIEW)

1CLR 1 1D 2

1CLK 3 1PRE 4

1Q 5 1Q 6 GND 7

14 VCC 13 2CLR 12 2D 11 2CLK 10 2PRE 9 2Q 8 2Q description

The SN74AHC74Q dual positive-edge-triggered device is a D-type flip-flop.

A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs, regardless of the levels of the other inputs. When PRE and CLR are inactive (high), data at the data (D) input meeting the setup time requirements is transferred to the outputs on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level and is not directly related to the rise time of the clock pulse. Following the hold-time interval, data at the D input can be changed without affecting the levels at the outputs.

ORDERING INFORMATION{

PACKAGE‡

ORDERABLE PART NUMBER

TOP-SIDE MARKING

SOIC

- D

- 40°C to 125°C

TSSOP

- PW

Tape and reel Tape and reel

SN74AHC74QDRQ1 AHC74Q SN74AHC74QPWRQ1 HA74Q

† For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at http://.ti.. ‡ Package drawings, thermal data, and symbolization are available at http://.ti./packaging....