SN74ALS996 Overview

Key Specifications

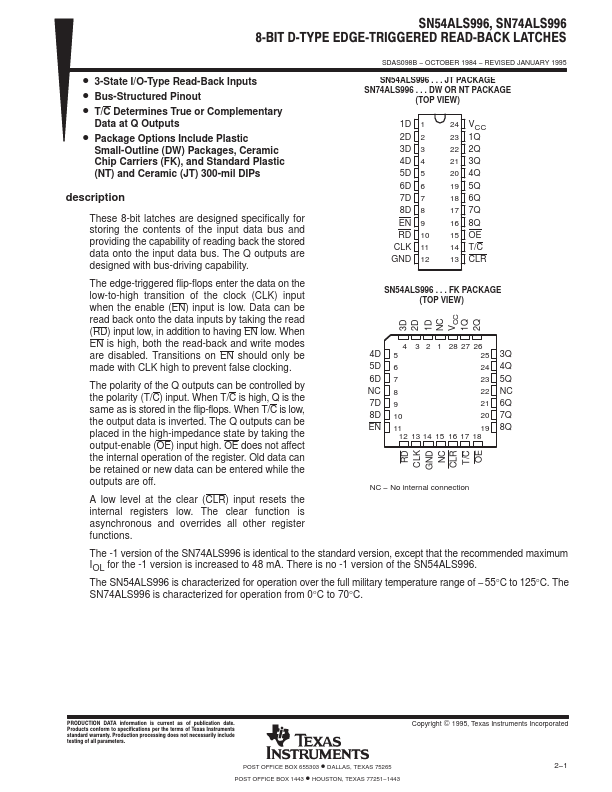

Package: SOIC

Mount Type: Surface Mount

Pins: 24

Operating Voltage: 5 V

Description

These 8-bit latches are designed specifically for storing the contents of the input data bus and providing the capability of reading back the stored data onto the input data bus. The Q outputs are designed with bus-driving capability.