SN74ALVCH162841 Overview

Key Specifications

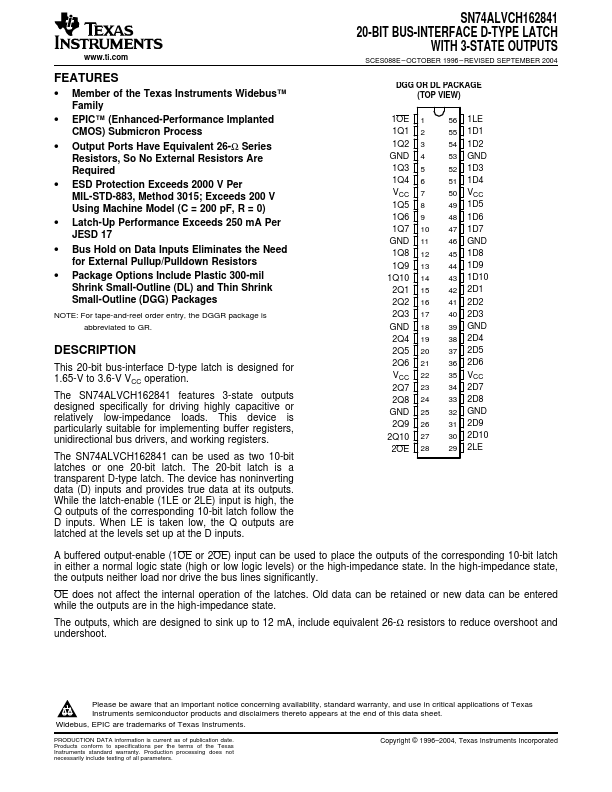

Package: SSOP

Mount Type: Surface Mount

Pins: 56

Max Voltage (typical range): 3.6 V

Description

This 20-bit bus-interface D-type latch is designed for 1.65-V to 3.6-V VCC operation. The SN74ALVCH162841 features 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads.

Key Features

- Member of the Texas Instruments Widebus™ Family

- EPIC™ (Enhanced-Performance Implanted CMOS) Submicron Process

- Output Ports Have Equivalent 26-Ω Series Resistors, So No External Resistors Are Required

- ESD Protection Exceeds 2000 V Per MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R =

- Latch-Up Performance Exceeds 250 mA Per JESD 17