SN74ALVCH16721 Overview

Key Specifications

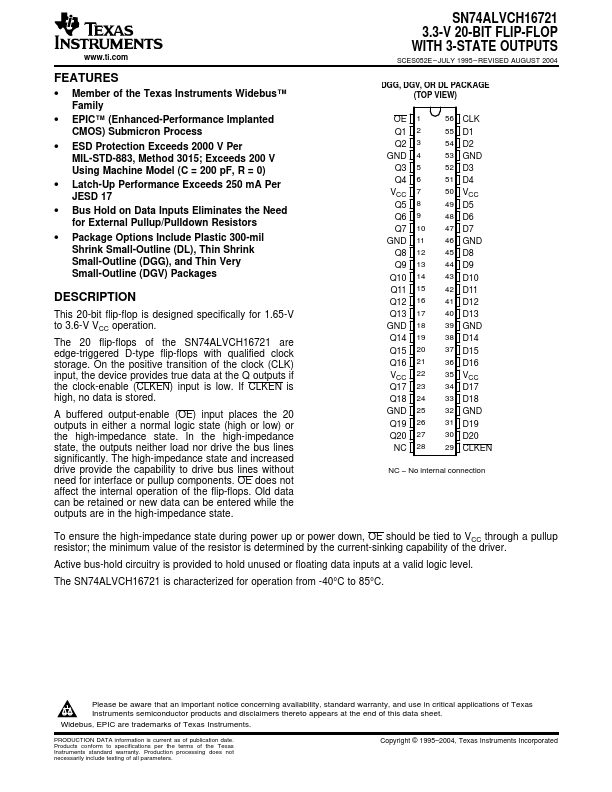

Package: TSSOP

Mount Type: Surface Mount

Pins: 56

Operating Voltage: 3.3 V

Description

This 20-bit flip-flop is designed specifically for 1.65-V to 3.6-V VCC operation. The 20 flip-flops of the SN74ALVCH16721 are edge-triggered D-type flip-flops with qualified clock storage.

Key Features

- Member of the Texas Instruments Widebus™ Family

- EPIC™ (Enhanced-Performance Implanted CMOS) Submicron Process

- ESD Protection Exceeds 2000 V Per MIL-STD-883, Method 3015; Exceeds 200 V Using Machine Model (C = 200 pF, R =

- Latch-Up Performance Exceeds 250 mA Per JESD 17

- Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors