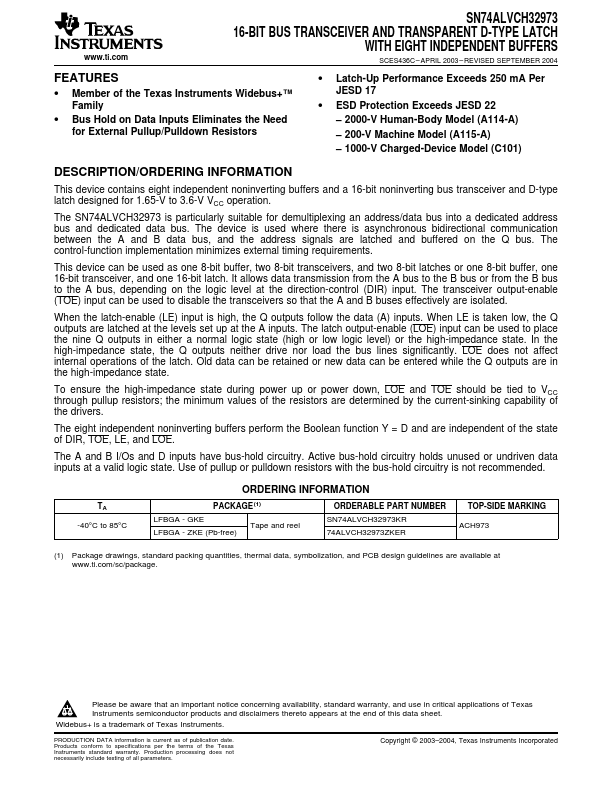

SN74ALVCH32973 Overview

Key Specifications

Package: BGA

Mount Type: Surface Mount

Pins: 96

Max Voltage (typical range): 3.6 V

Key Features

- Member of the Texas Instruments Widebus+™ Family

- Bus Hold on Data Inputs Eliminates the Need for External Pullup/Pulldown Resistors

- Latch-Up Performance Exceeds 250 mA Per JESD 17

- ESD Protection Exceeds JESD 22 – 2000-V Human-Body Model (A114-A) – 200-V Machine Model (A115-A) – 1000-V Charged-Device Model (C101)