SN74AUP1G32 Overview

Key Specifications

Package: SOT-23

Mount Type: Surface Mount

Pins: 5

Max Voltage (typical range): 3.6 V

Description

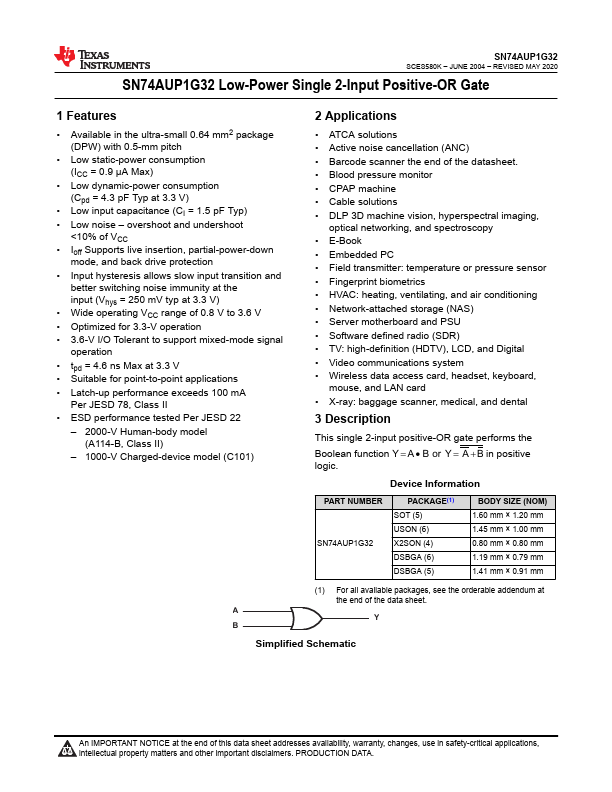

This single 2-input positive-OR gate performs the Boolean function Y = A - B or Y = A +B in positive logic. Device Information PART NUMBER SN74AUP1G32 PACKAGE(.

Key Features

- Available in the ultra-small 0.64 mm2 package (DPW) with 0.5-mm pitch

- Low static-power consumption (ICC = 0.9 µA Max)

- Low dynamic-power consumption (Cpd = 4.3 pF Typ at 3.3 V)

- Low input capacitance (CI = 1.5 pF Typ)

- Low noise – overshoot and undershoot <10% of VCC