SN74HCT138N

Description

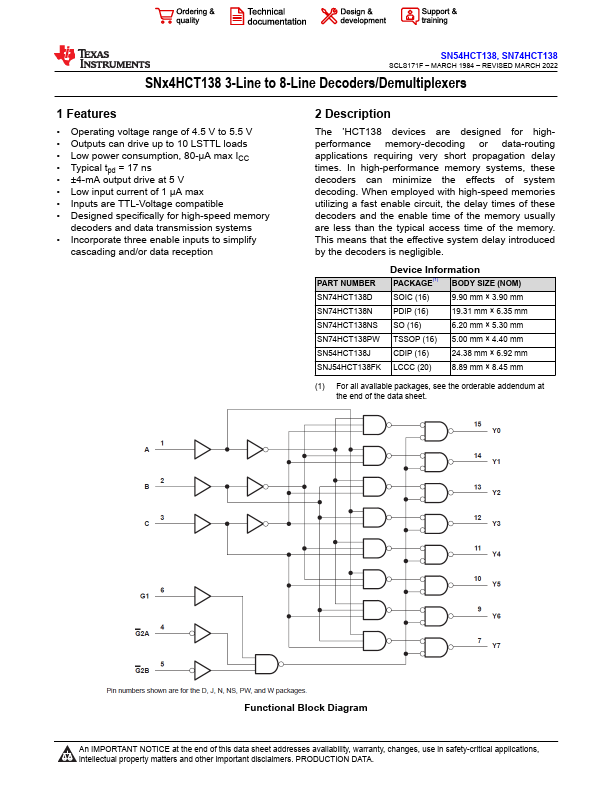

The ’HCT138 devices are designed for highperformance memory-decoding or data-routing applications requiring very short propagation delay times. In high-performance memory systems, these decoders can minimize the effects of system decoding.

Key Features

- Operating voltage range of 4.5 V to 5.5 V

- Outputs can drive up to 10 LSTTL loads

- Low power consumption, 80-µA max ICC

- Typical tpd = 17 ns

- ±4-mA output drive at 5 V

- Low input current of 1 µA max

- Inputs are TTL-Voltage compatible

- Designed specifically for high-speed memory decoders and data transmission systems

- Incorporate three enable inputs to simplify cascading and/or data reception