SN74LV10A Overview

Key Specifications

Package: SOIC

Mount Type: Surface Mount

Pins: 14

Max Voltage (typical range): 5.5 V

Description

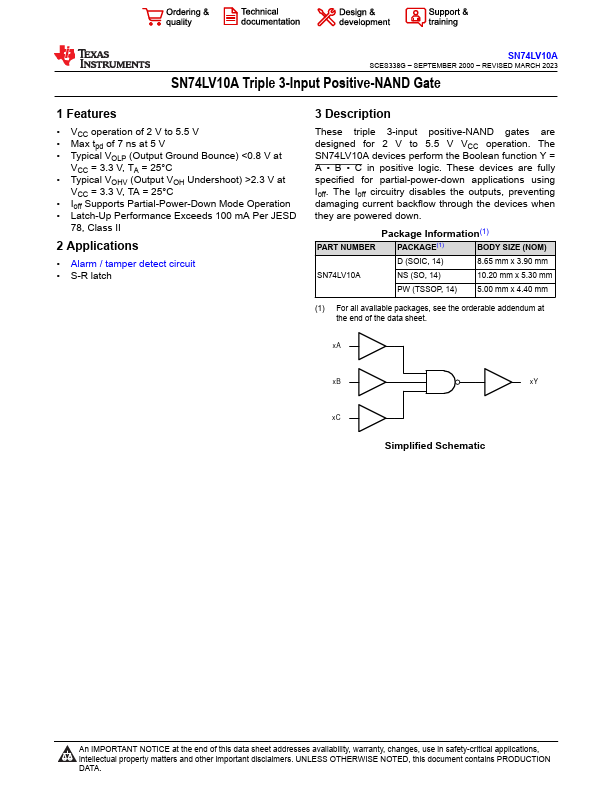

These triple 3-input positive-NAND gates are designed for 2 V to 5.5 V VCC operation. The SN74LV10A devices perform the Boolean function Y = A - B - C in positive logic.

Key Features

- VCC operation of 2 V to 5.5 V

- Max tpd of 7 ns at 5 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) >2.3 V at VCC = 3.3 V, TA = 25°C

- Ioff Supports Partial-Power-Down Mode Operation