SN74LV240A

Description

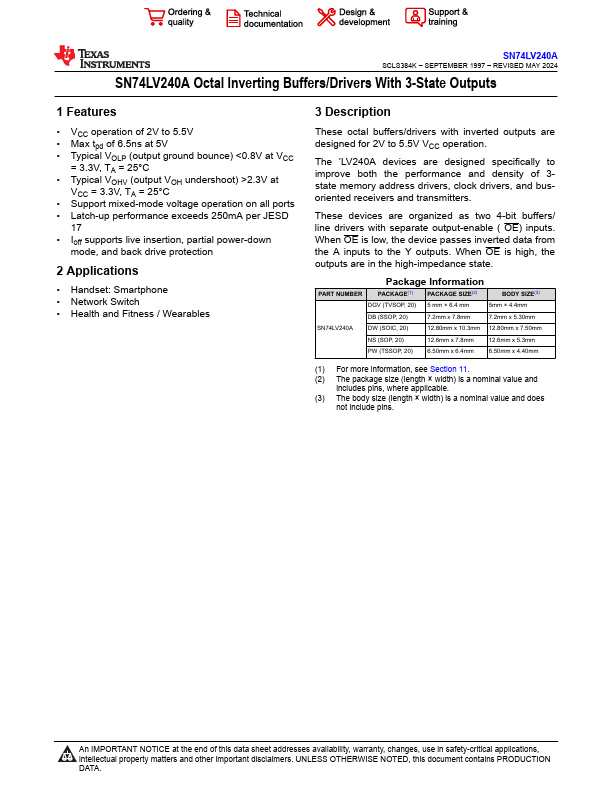

These octal buffers/drivers with inverted outputs are designed for 2V to 5.5V VCC operation. The ’LV240A devices are designed specifically to improve both the performance and density of 3state memory address drivers, clock drivers, and busoriented receivers and transmitters.

Key Features

- VCC operation of 2V to 5.5V

- Max tpd of 6.5ns at 5V

- Typical VOLP (output ground bounce) <0.8V at VCC = 3.3V, TA = 25°C

- Typical VOHV (output VOH undershoot) >2.3V at VCC = 3.3V, TA = 25°C

- Support mixed-mode voltage operation on all ports

- Latch-up performance exceeds 250mA per JESD 17

- Ioff supports live insertion, partial power-down mode, and back drive protection