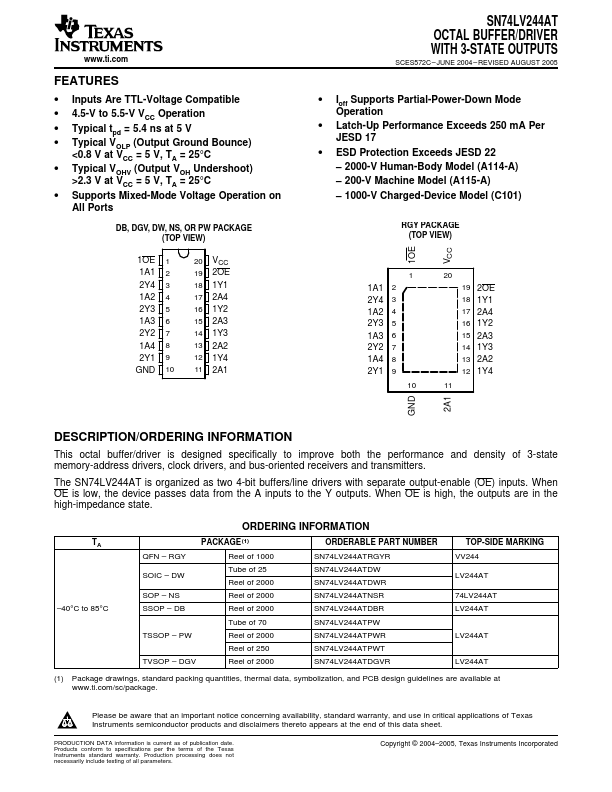

SN74LV244AT

Key Features

- Inputs Are TTL-Voltage Compatible

- 4.5-V to 5.5-V VCC Operation

- Typical tpd = 5.4 ns at 5 V

- Typical VOLP (Output Ground Bounce) <0.8 V at VCC = 5 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) >2.3 V at VCC = 5 V, TA = 25°C

- Supports Mixed-Mode Voltage Operation on All Ports