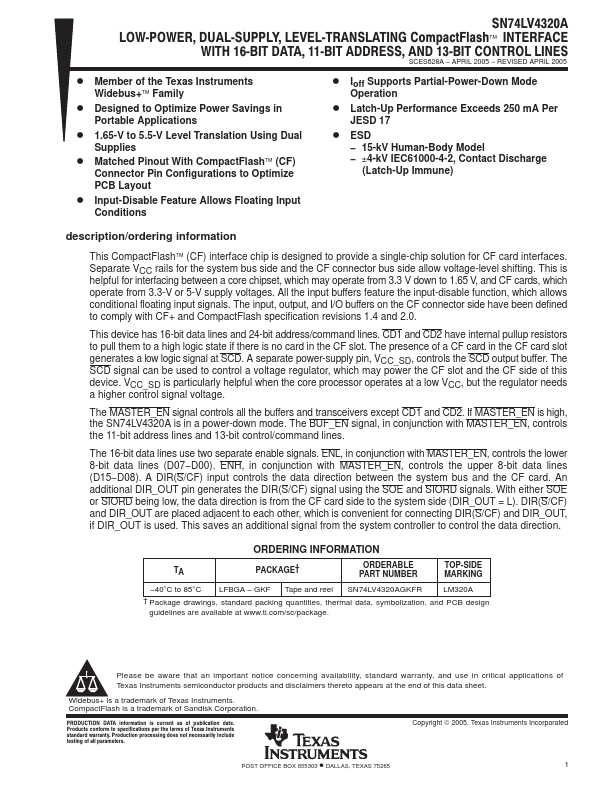

| Part | SN74LV4320A |

|---|---|

| Description | LEVEL-TRANSLATING COMPACTFLASH INTERFACE |

| Manufacturer | Texas Instruments |

| Size | 1.01 MB |

Pricing from 2.66 USD, available from Rochester Electronics and DigiKey.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 35195 | 25+ : 2.66 USD 100+ : 2.53 USD 500+ : 2.39 USD 1000+ : 2.26 USD |

View Offer |

| DigiKey | 6 | 1+ : 5.21 USD | View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| AN214 | Microchip Technology | Smart Transducer Interface |

| AiP650E | I-CORE | 2-line Serial Interface/Common Cathode 8Seg 4Grid LED Controller/Driver |

| XT2052 | Silinktek | 1A Is Compatible With the USB Interface Linear Battery Management |