SN74LVC112A Overview

Key Specifications

Package: SOIC

Mount Type: Surface Mount

Pins: 16

Max Voltage (typical range): 3.6 V

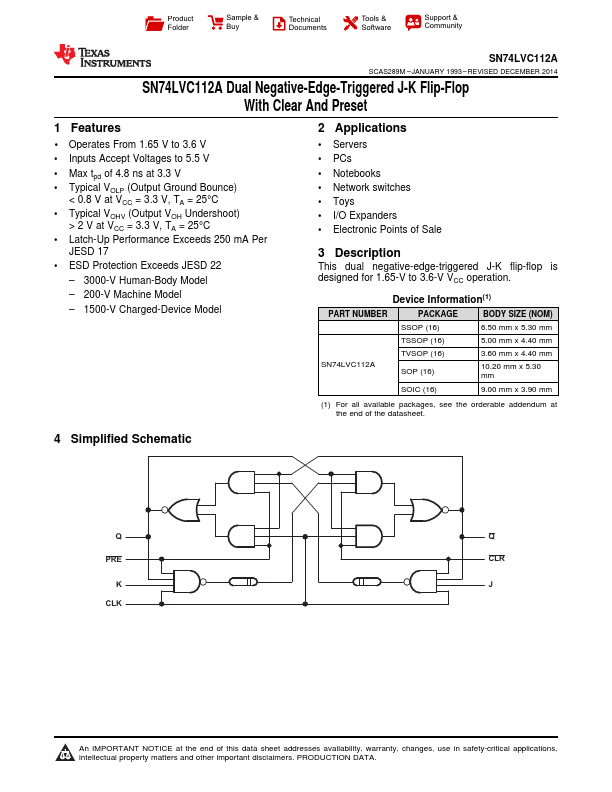

Description

This dual negative-edge-triggered J-K flip-flop is designed for 1.65-V to 3.6-V VCC operation. Device Information(1) PART NUMBER PACKAGE BODY SIZE (NOM) SSOP (16) 6.50 mm x 5.30 mm TSSOP (16) 5.00 mm x 4.40 mm SN74LVC112A TVSOP (16) SOP (16) 3.60 mm x 4.40 mm 10.20 mm x 5.30 mm SOIC (16) 9.00 mm x 3.90 mm (1) For all available packages, see the orderable addendum at the end of the datasheet.

Key Features

- 1 Operates From 1.65 V to 3.6 V

- Inputs Accept Voltages to 5.5 V

- Max tpd of 4.8 ns at 3.3 V

- Typical VOLP (Output Ground Bounce) < 0.8 V at VCC = 3.3 V, TA = 25°C

- Typical VOHV (Output VOH Undershoot) > 2 V at VCC = 3.3 V, TA = 25°C