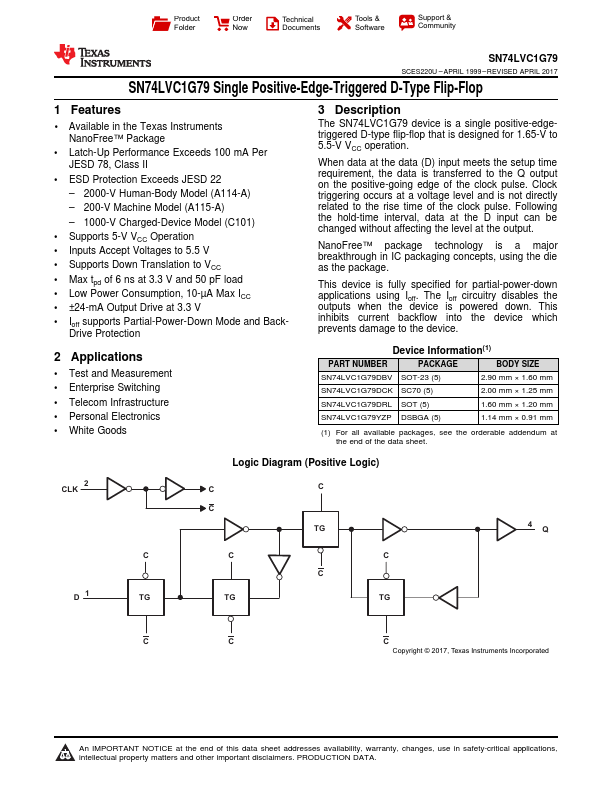

| Part | SN74LVC1G79 |

|---|---|

| Description | Single Positive-Edge-Triggered D-Type Flip-Flop |

| Manufacturer | Texas Instruments |

| Size | 1.47 MB |

Pricing from 0.18 USD, available from Rochester Electronics and DigiKey.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Rochester Electronics | 45750 | 100+ : 0.18 USD 500+ : 0.162 USD 1000+ : 0.1494 USD 10000+ : 0.1332 USD |

View Offer |

| DigiKey | 7922 | 1+ : 0.36 USD 10+ : 0.253 USD 25+ : 0.2248 USD 100+ : 0.194 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| CD40175BC | Fairchild Semiconductor | Hex D-Type Flip-Flop / Quad D-Type Flip-Flop |

| K561TM2 | Unknown Manufacturer | 2-stage (Master-slave) D flip-flop |

| 74LS74 | Texas Instruments | Dual D-Type Positive-Edge-Triggered Flip-Flop |