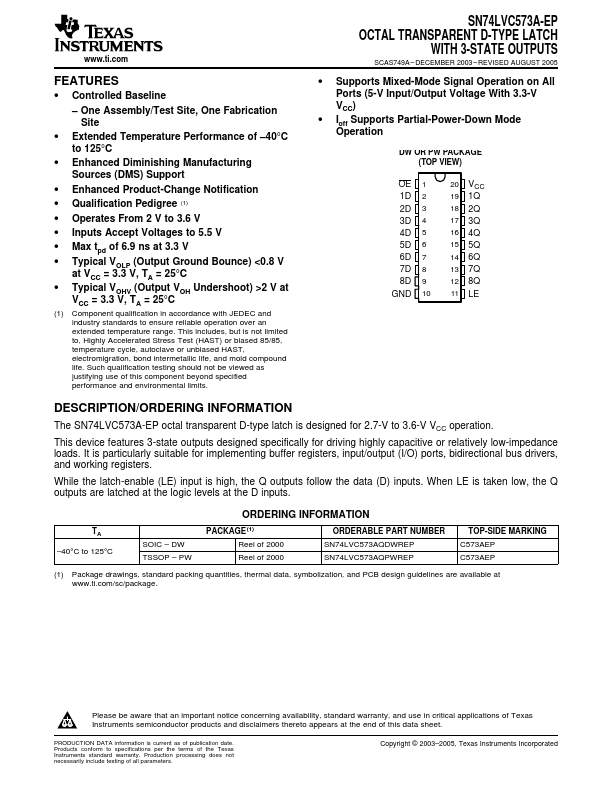

SN74LVC573A-EP Overview

Key Specifications

Output Type (varies by manufacturer): CMOS

Key Features

- Controlled Baseline – One Assembly/Test Site, One Fabrication Site

- Extended Temperature Performance of –40°C to 125°C

- Enhanced Diminishing Manufacturing Sources (DMS) Support

- Enhanced Product-Change Notification

- Qualification Pedigree (1)