SN74LVCH32373A Overview

Key Specifications

Pins: 96

Height: 1.4 mm

Length: 13.5 mm

Width: 5.5 mm

Description

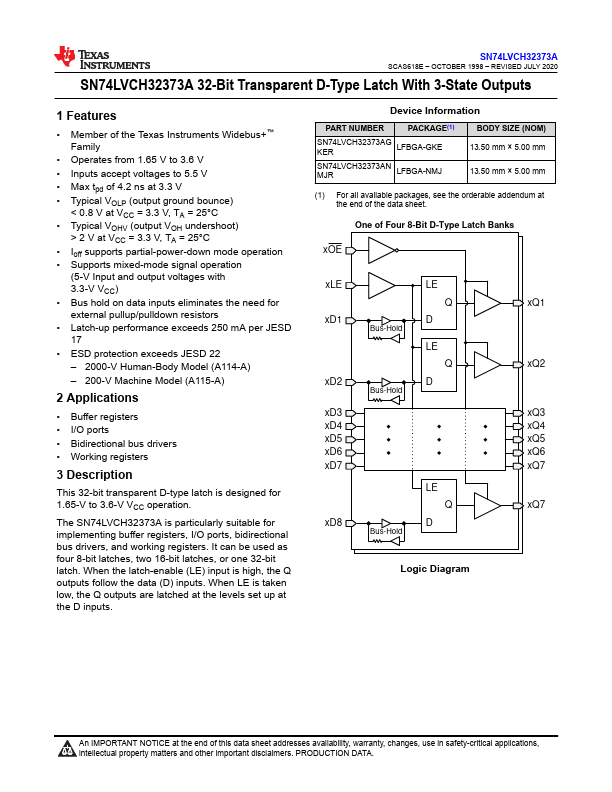

This 32-bit transparent D-type latch is designed for 1.65-V to 3.6-V VCC operation. The SN74LVCH32373A is particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

Key Features

- Member of the Texas Instruments Widebus+™ Family

- Operates from 1.65 V to 3.6 V

- Inputs accept voltages to 5.5 V

- Max tpd of 4.2 ns at 3.3 V

- Typical VOLP (output ground bounce) < 0.8 V at VCC = 3.3 V, TA = 25°C