SN74LVT125 Overview

Key Specifications

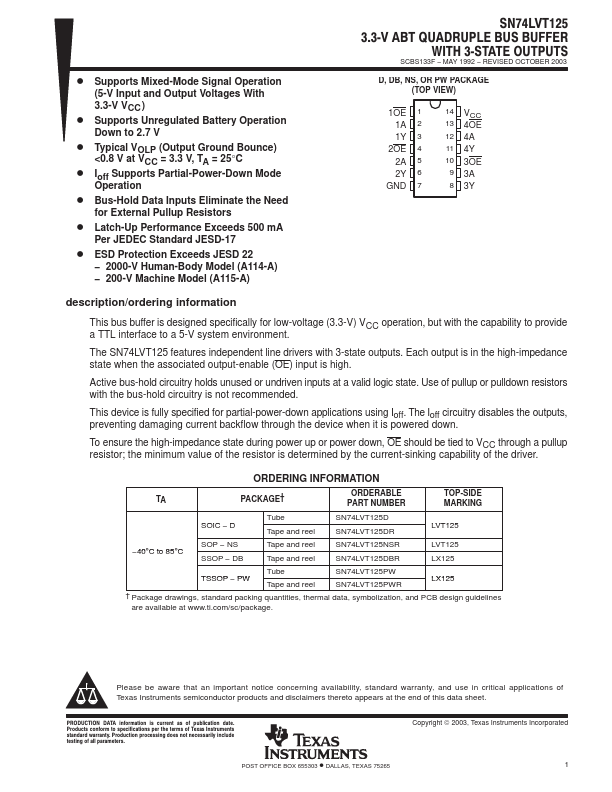

Package: SOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 3.3 V

Key Features

- independent line drivers with 3-state outputs

- Each output is in the high-impedance state when the associated output-enable (OE) input is high

- Active bus-hold circuitry holds unused or undriven inputs at a valid logic state

- Use of pullup or pulldown resistors with the bus-hold circuitry is not recommended

- This device is fully specified for partial-power-down applications using Ioff