SN75LVDS388A

Overview

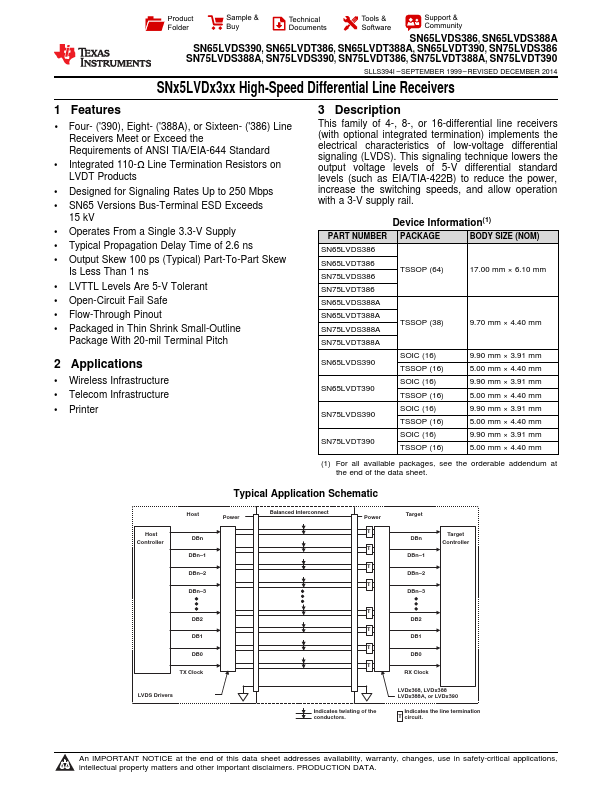

This family of 4-, 8-, or 16-differential line receivers (with optional integrated termination) implements the electrical characteristics of low-voltage differential signaling (LVDS). This signaling technique lowers the output voltage levels of 5-V differential standard levels (such as EIA/TIA-422B) to reduce the power, increase the switching speeds, and allow operation with a 3-V supply rail.

- 1 Four- ('390), Eight- ('388A), or Sixteen- ('386) Line Receivers Meet or Exceed the Requirements of ANSI TIA/EIA-644 Standard

- Integrated 110-Ω Line Termination Resistors on LVDT Products

- Designed for Signaling Rates Up to 250 Mbps

- SN65 Versions Bus-Terminal ESD Exceeds 15 kV

- Operates From a Single 3.3-V Supply

- Typical Propagation Delay Time of 2.6 ns

- Output Skew 100 ps (Typical) Part-To-Part Skew Is Less Than 1 ns

- LVTTL Levels Are 5-V Tolerant

- Open-Circuit Fail Safe

- Flow-Through Pinout