| Part | SNJ54HC109W |

|---|---|

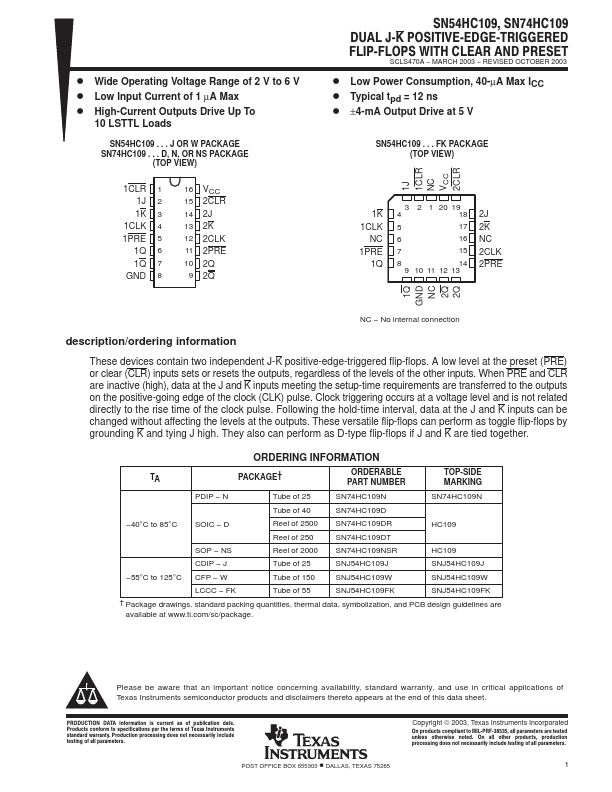

| Description | DUAL J-K POSITIVE-EDGE-TRIGGERED FLIP-FLOPS |

| Manufacturer | Texas Instruments |

| Size | 1.08 MB |

Pricing from 39.946 USD, available from Texas Instruments and Win Source.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Texas Instruments | 0 | 1+ : 39.946 USD 100+ : 34.893 USD 250+ : 26.904 USD 1000+ : 24.064 USD |

View Offer |

| Win Source | 1000 | 1+ : 71.5701 USD 2+ : 58.7242 USD 3+ : 56.889 USD 4+ : 55.0539 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| 74LS74 | Hitachi Semiconductor | Dual D-type Positive Edge-triggered Flip-Flops |

| 7476 | Fairchild Semiconductor | Dual Master-Slave J-K Flip-Flops |

| 7474 | Fairchild Semiconductor | Dual Positive-Edge-Triggered D-Type Flip-Flops |