TMS320C6747

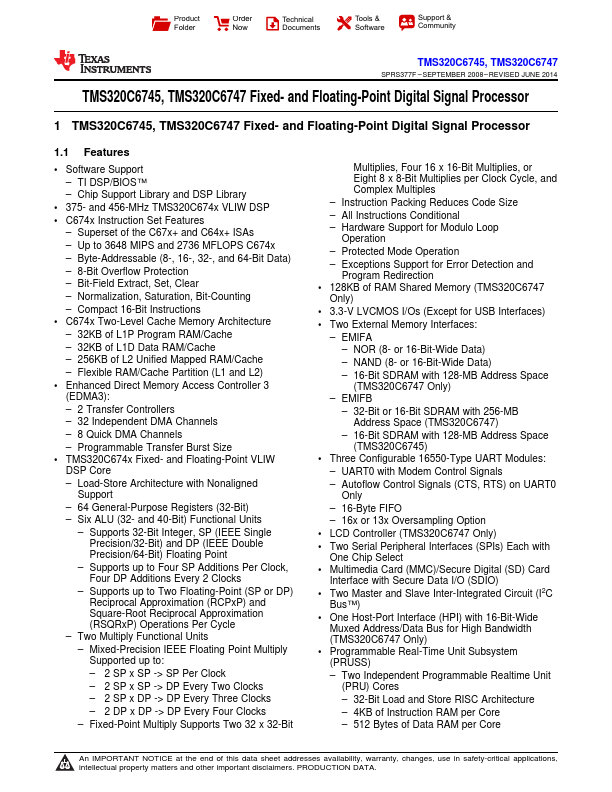

Features

- Software Support

- TI DSP/BIOS™

- Chip Support Library and DSP Library

- 375- and 456-MHz TMS320C674x VLIW DSP

- C674x Instruction Set Features

- Superset of the C67x+ and C64x+ ISAs

- Up to 3648 MIPS and 2736 MFLOPS C674x

- Byte-Addressable (8-, 16-, 32-, and 64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- Normalization, Saturation, Bit-Counting

- pact 16-Bit Instructions

- C674x Two-Level Cache Memory Architecture

- 32KB of L1P Program RAM/Cache

- 32KB of L1D Data RAM/Cache

- 256KB of L2 Unified Mapped RAM/Cache

- Flexible RAM/Cache Partition (L1 and L2)

- Enhanced Direct Memory Access Controller 3 (EDMA3):

- 2 Transfer Controllers

- 32 Independent DMA Channels

- 8 Quick DMA Channels

- Programmable Transfer Burst Size

- TMS320C674x Fixed- and Floating-Point VLIW DSP Core

- Load-Store Architecture with Nonaligned

Support

- 64 General-Purpose Registers (32-Bit)

- Six ALU (32- and 40-Bit) Functional Units

- Supports 32-Bit Integer, SP (IEEE...