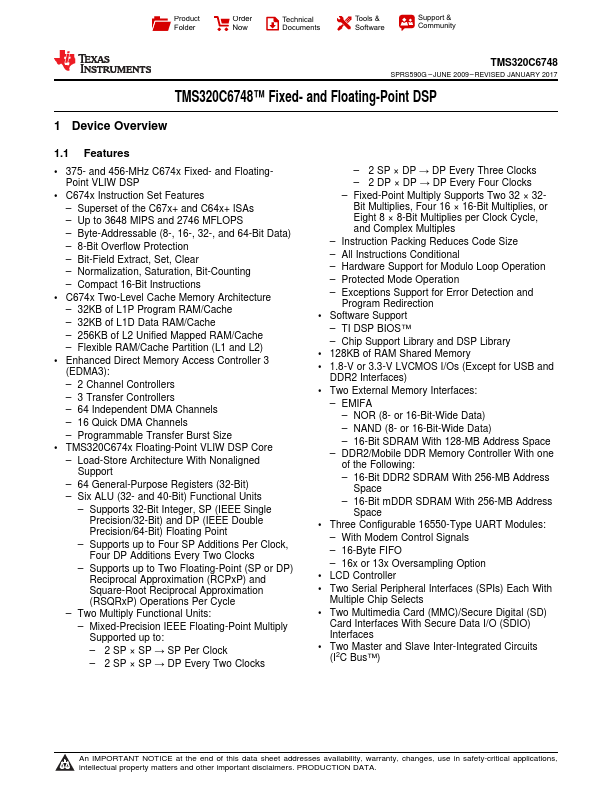

| Part | TMS320C6748 |

|---|---|

| Description | Fixed- and Floating-Point DSP |

| Manufacturer | Texas Instruments |

| Size | 2.14 MB |

Pricing from 28.7 USD, available from Arrow Electronics and DigiKey.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| Arrow Electronics | 140 | 1+ : 28.7 USD 10+ : 25.84 USD 25+ : 24.83 USD 100+ : 23.85 USD |

View Offer |

| DigiKey | 135 | 1+ : 27.94 USD 10+ : 22.539 USD 25+ : 21.1888 USD 160+ : 19.31944 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| ACM8628M | ACME | Digital Input Amplifier Built-in DSP |

| RK2118M | Rockchip | high-performance triple-core HiFi4 DSP processor |

| DU561 | MVSILICON | High-performance Audio DSP |