TPIC5323L

TPIC5323L is logic-level power DMOS array manufactured by Texas Instruments.

description

DRAIN3 6 11 SOURCE3

The TPIC5323L is a monolithic gate-protected logic-level power DMOS array that consists of

DRAIN3 7 GND 8

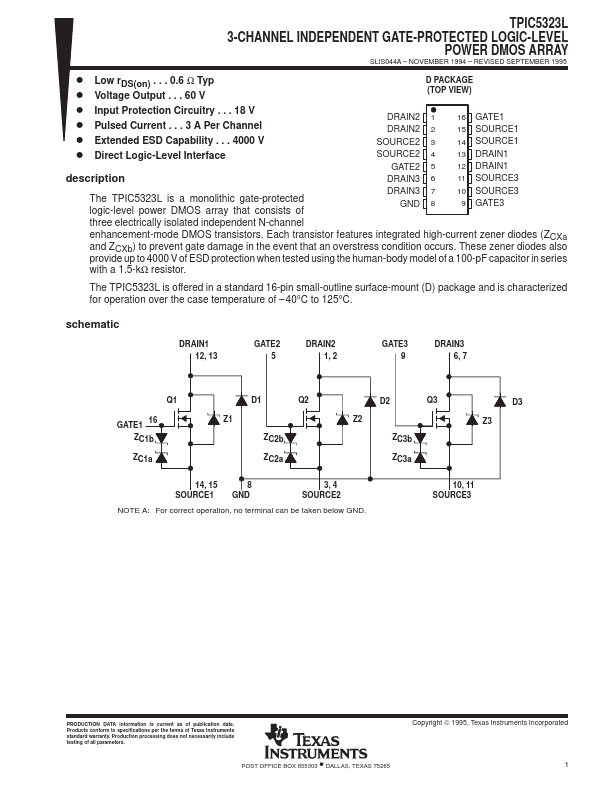

10 SOURCE3 9 GATE3 three electrically isolated independent N-channel enhancement-mode DMOS transistors. Each transistor features integrated high-current zener diodes (ZCXa and ZCXb) to prevent gate damage in the event that an overstress condition occurs. These zener diodes also provide up to 4000 V of ESD protection when tested using the human-body model of a 100-p F capacitor in series with a 1.5-kΩ resistor.

The TPIC5323L is offered in a standard 16-pin small-outline surface-mount (D) package and is characterized for operation over the case temperature of

- 40°C to 125°C. schematic

DRAIN1 12, 13

GATE2 5

DRAIN2 1, 2

GATE3 9

DRAIN3 6, 7

Q1

GATE1 16 ZC1b ZC1a

D1 Q2 Z1

ZC2b ZC2a

D2 Q3 Z2

ZC3b ZC3a

D3 Z3

14, 15

SOURCE1 GND

3, 4 SOURCE2

NOTE A: For correct operation, no terminal can be taken below GND.

10, 11 SOURCE3

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

- POST OFFICE BOX 655303 DALLAS, TEXAS 75265

Copyright © 1995, Texas Instruments Incorporated 1

TPIC5323L 3-CHANNEL INDEPENDENT GATE-PROTECTED

SLIS044A

- NOVEMBER 1994

- REVISED SEPTEMBER 1995 absolute maximum ratings over operating case temperature range (unless otherwise noted)† Drain-to-source voltage, VDS

- -

- -

- -

- -

- -

- - . . 60 V Source-to-GND voltage

- -

-...