74ALVC14PW

74ALVC14PW is Hex inverting Schmitt trigger manufactured by Nexperia.

- Part of the 74ALVC14 comparator family.

- Part of the 74ALVC14 comparator family.

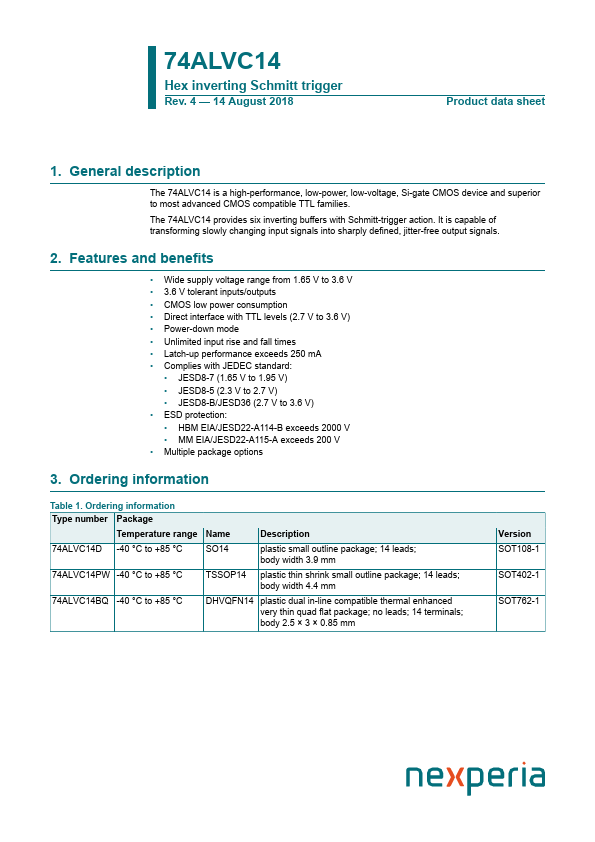

74ALVC14

Hex inverting Schmitt trigger

Rev. 4

- 14 August 2018

Product data sheet

1. General description

The 74ALVC14 is a high-performance, low-power, low-voltage, Si-gate CMOS device and superior to most advanced CMOS patible TTL families.

The 74ALVC14 provides six inverting buffers with Schmitt-trigger action. It is capable of transforming slowly changing input signals into sharply defined, jitter-free output signals.

2. Features and benefits

- Wide supply voltage range from 1.65 V to 3.6 V

- 3.6 V tolerant inputs/outputs

- CMOS low power consumption

- Direct interface with TTL levels (2.7 V to 3.6 V)

- Power-down mode

- Unlimited input rise and fall times

- Latch-up performance...