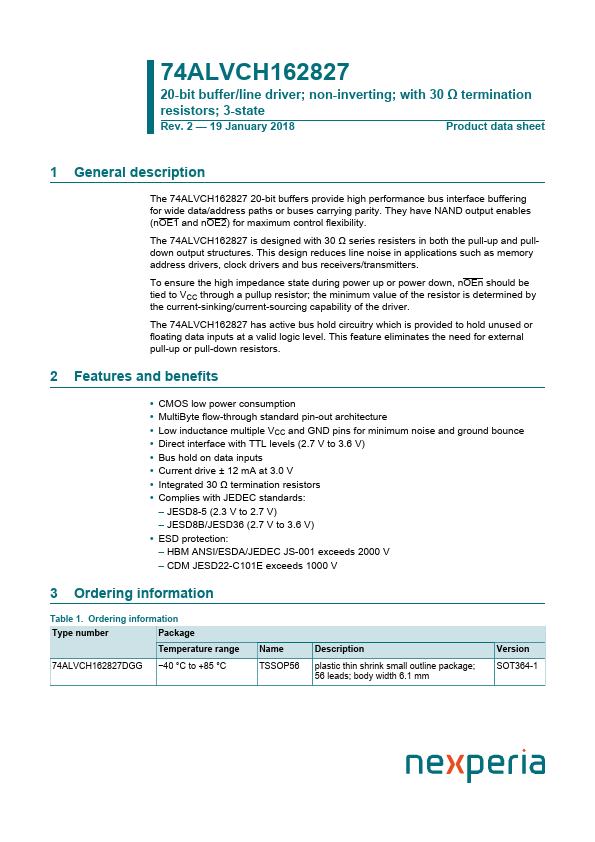

74ALVCH162827

74ALVCH162827 is 20-bit buffer/line driver manufactured by Nexperia.

20-bit buffer/line driver; non-inverting; with 30 Ω termination resistors; 3-state

Rev. 2

- 19 January 2018

Product data sheet

1 General description

The 74ALVCH162827 20-bit buffers provide high performance bus interface buffering for wide data/address paths or buses carrying parity. They have NAND output enables (nOE1 and nOE2) for maximum control flexibility.

The 74ALVCH162827 is designed with 30 Ω series resisters in both the pull-up and pulldown output structures. This design reduces line noise in applications such as memory address drivers, clock drivers and bus receivers/transmitters.

To ensure the high impedance state during power up or power down, nOEn should be...