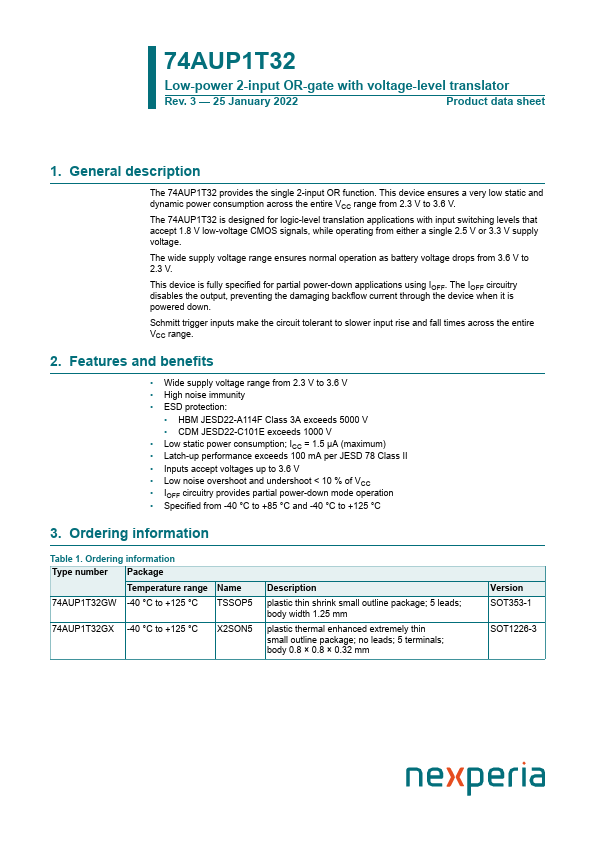

74AUP1T32

74AUP1T32 is Low-power 2-input OR-gate manufactured by Nexperia.

Low-power 2-input OR-gate with voltage-level translator

Rev. 3

- 25 January 2022

Product data sheet

1. General description

The 74AUP1T32 provides the single 2-input OR function. This device ensures a very low static and dynamic power consumption across the entire VCC range from 2.3 V to 3.6 V.

The 74AUP1T32 is designed for logic-level translation applications with input switching levels that accept 1.8 V low-voltage CMOS signals, while operating from either a single 2.5 V or 3.3 V supply voltage.

The wide supply voltage range ensures normal operation as battery voltage drops from 3.6 V to 2.3 V.

This device is fully specified for partial power-down applications using IOFF....