74HC173D

74HC173D is Quad D-type flip-flop manufactured by Nexperia.

- Part of the 74HC173 comparator family.

- Part of the 74HC173 comparator family.

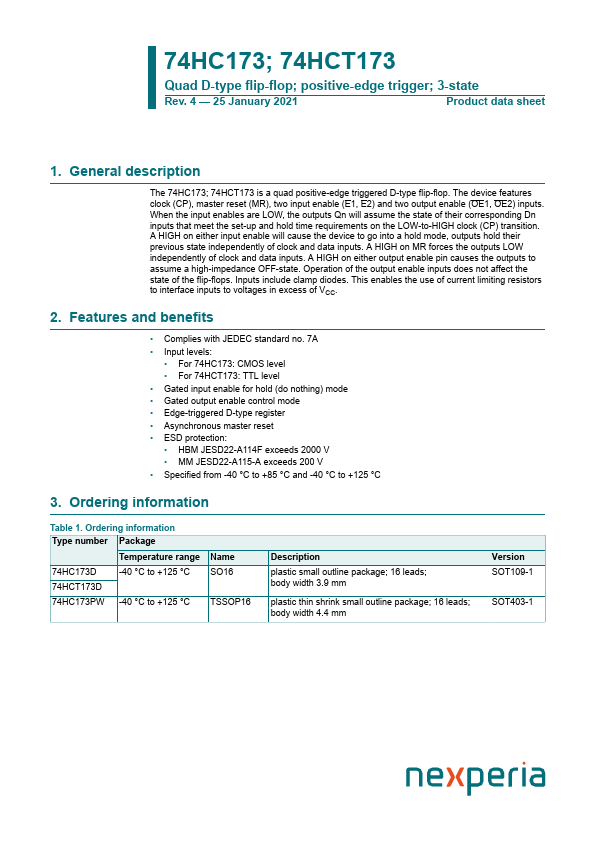

74HC173; 74HCT173

Quad D-type flip-flop; positive-edge trigger; 3-state

Rev. 4

- 25 January 2021

Product data sheet

1. General description

The 74HC173; 74HCT173 is a quad positive-edge triggered D-type flip-flop. The device Features clock (CP), master reset (MR), two input enable (E1, E2) and two output enable (OE1, OE2) inputs. When the input enables are LOW, the outputs Qn will assume the state of their corresponding Dn inputs that meet the set-up and hold time requirements on the LOW-to-HIGH clock (CP) transition. A HIGH on either input enable will cause the device to go into a hold mode, outputs hold their previous state independently of clock and data inputs. A HIGH on MR forces...