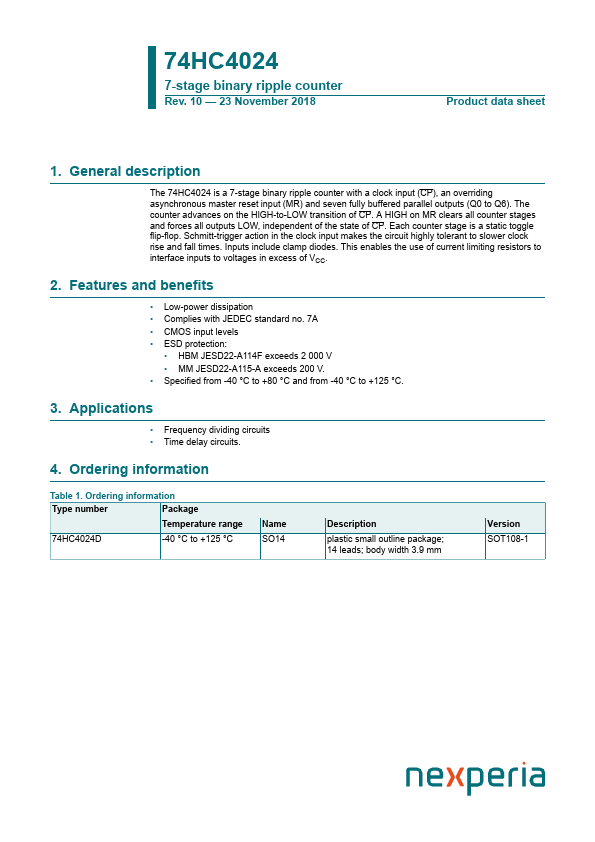

74HC4024D Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 14

Operating Voltage: 5 V

Description

The 74HC4024 is a 7-stage binary ripple counter with a clock input (CP), an overriding asynchronous master reset input (MR) and seven fully buffered parallel outputs (Q0 to Q6). The counter advances on the HIGH-to-LOW transition of CP.

Key Features

- Low-power dissipation

- Complies with JEDEC standard no. 7A

- CMOS input levels

- ESD protection

- MM JESD22-A115-A exceeds 200 V