74HCT175-Q100 Overview

Description

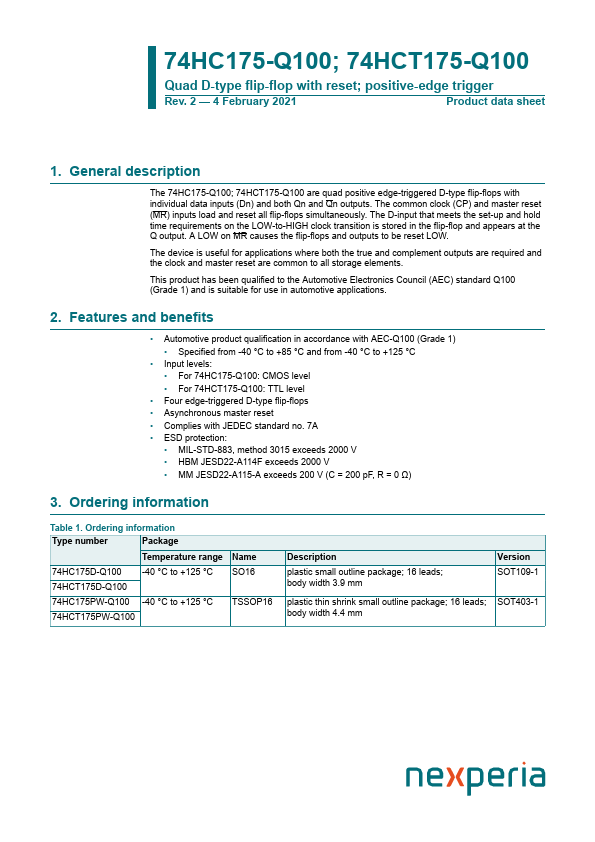

The 74HC175-Q100; 74HCT175-Q100 are quad positive edge-triggered D-type flip-flops with individual data inputs (Dn) and both Qn and Qn outputs. The common clock (CP) and master reset (MR) inputs load and reset all flip-flops simultaneously.

Key Features

- Automotive product qualification in accordance with AEC-Q100 (Grade

- Specified from -40 °C to +85 °C and from -40 °C to +125 °C

- Input levels

- For 74HC175-Q100: CMOS level

- For 74HCT175-Q100: TTL level